# HY10P Family

User's Guide Mixed Signal Microcontroller

Embedded 18-Bit ΣΔADC 8-Bit RISC-like Mixed Signal Microcontroller

### **Table of Contents**

| 1.   | READING GUIDANCE                                          | 5  |

|------|-----------------------------------------------------------|----|

| 1.1. | Terms and Definition                                      | 6  |

| 2.   | CENTRAL PROCESSING UNIT (CPU)                             | 8  |

| 2.1. | CPU Core                                                  | 8  |

| 2.2. | Memory                                                    | 9  |

| 3.   | OSCILLATOR, CLOCK SOURCE AND POWER CONSUMPTION MANAGEMENT | 22 |

| 3.1. | Oscillator                                                | 22 |

| 3.2. | CPU and Peripheral Circuit Clock Source                   | 23 |

| 3.3. | Register Instruction-Working Clock Source Controller      | 26 |

| 3.4. | Power Consumption Management and Operation Status         | 29 |

| 4.   | RESET                                                     | 30 |

| 4.1. | Reset Event Description                                   | 30 |

| 4.2. | Status Register                                           | 32 |

| 4.3. | Register List-Data Memory Reset Status                    | 35 |

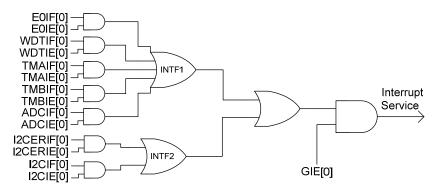

| 5.   | INTERRUPT                                                 | 37 |

| 5.1. | Register Instruction-Interrupt                            | 38 |

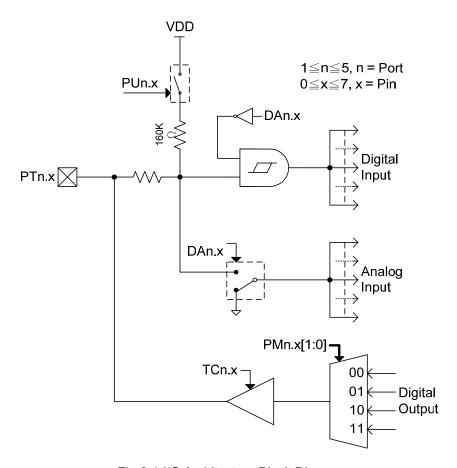

| 6.   | INPUT/ OUTPUT PORT (I/O)                                  | 40 |

| 6.1. | Introduction of PORT related register                     | 41 |

| 6.2. | Input/ Output Port 1, I/O Port1                           | 41 |

| 6.3. | Input/ Output Port 2, I/O Port2                           | 43 |

| 6.4. | Input/ Output Port 3,I/O Port3                            | 45 |

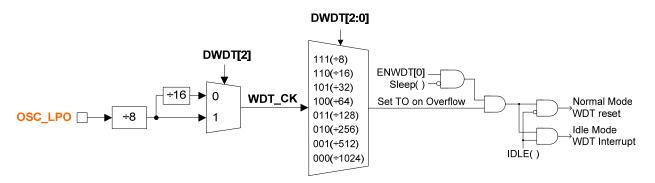

| 7.   | WATCH DOG TIMER                                           | 47 |

# Embedded 18-Bit ΣΔADC

### 8-Bit RISC-like Mixed Signal Microcontroller

| 7.1.         | WDT Manual                                    | 47  |

|--------------|-----------------------------------------------|-----|

| 7.2.         | Register Instruction-WDT                      | 49  |

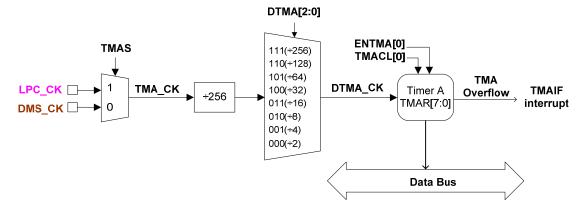

| 8. 1         | TIMER-A                                       | 50  |

| 8.1.         | Register Instruction-TMA                      | 51  |

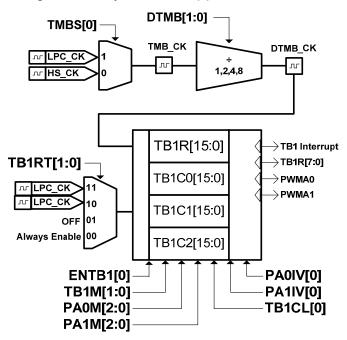

| 9. 1         | 16-BIT TIMER B (TMB)                          | 52  |

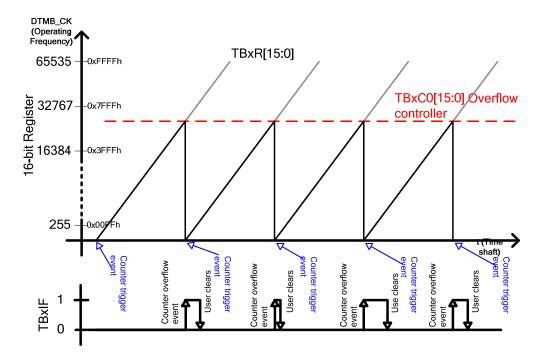

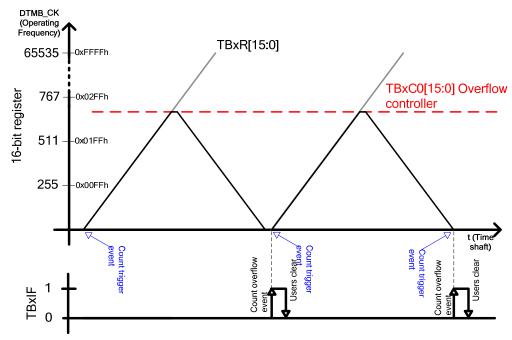

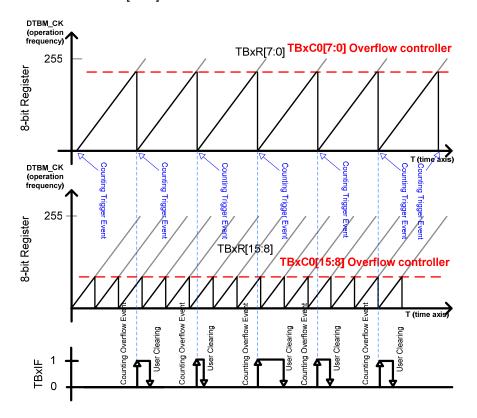

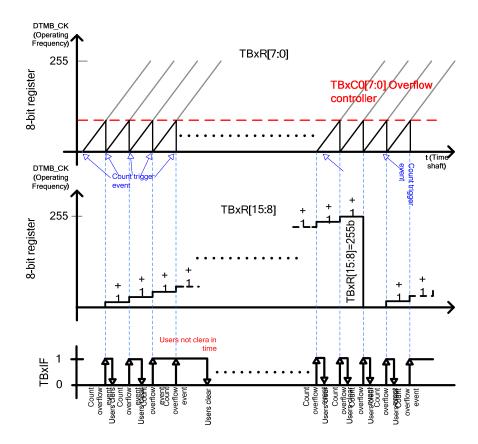

| 9.1.         | 4 Types Counting Modes of TMB                 | 54  |

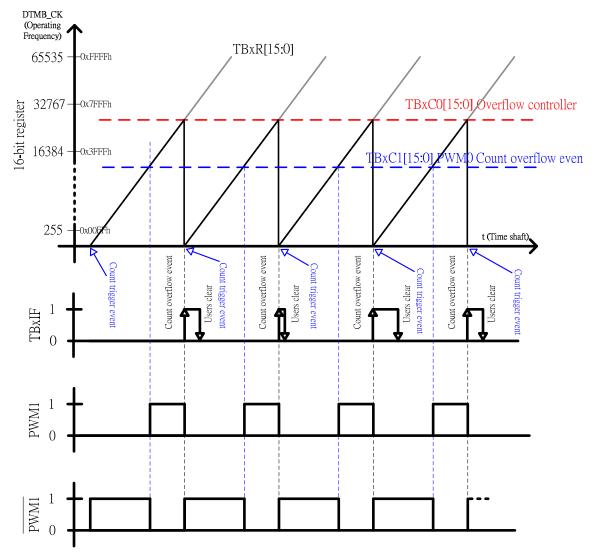

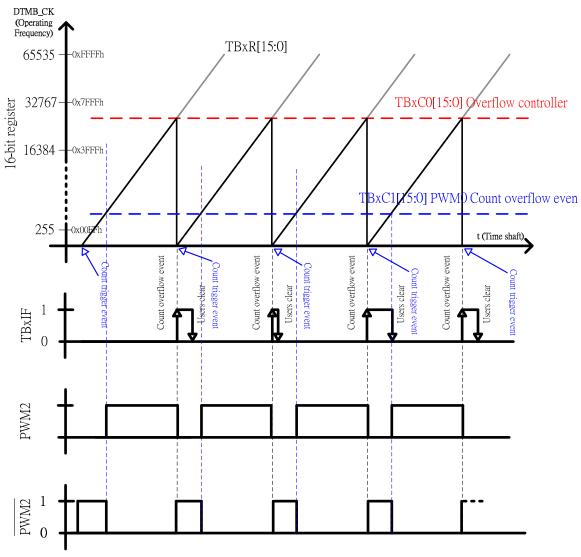

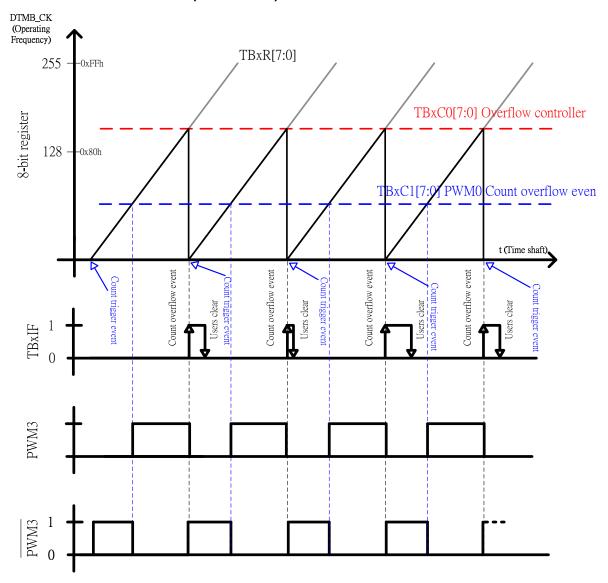

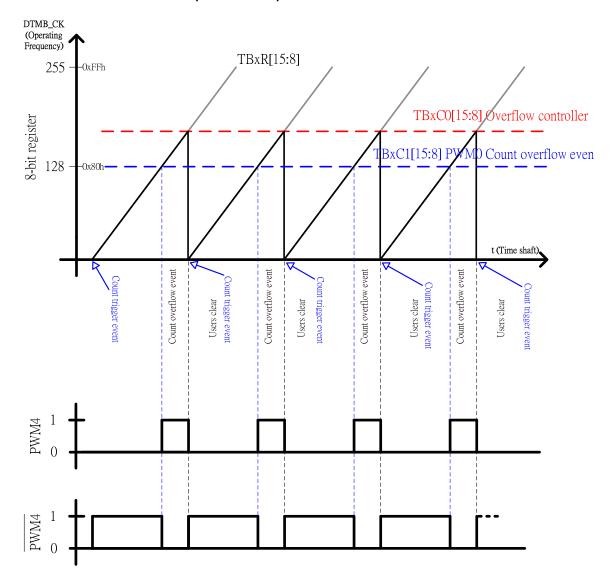

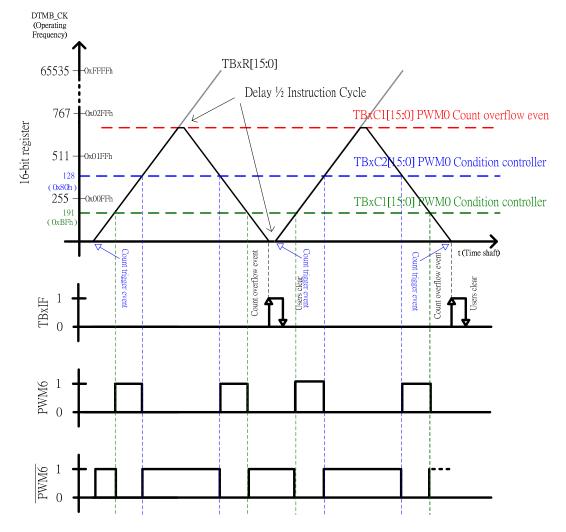

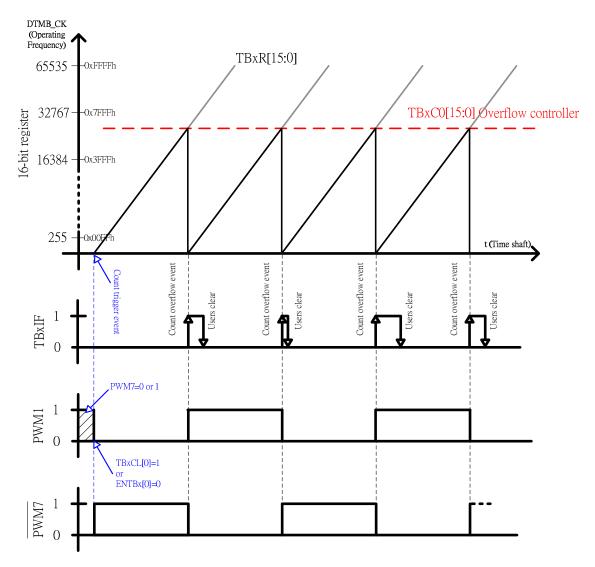

| 9.2.         | Pulse-Width Modulation (PWM)                  | 61  |

| 9.3.         | TMB1 Control Register List and Instructions:  | 74  |

| 10. F        | POWER SYSTEM                                  | 78  |

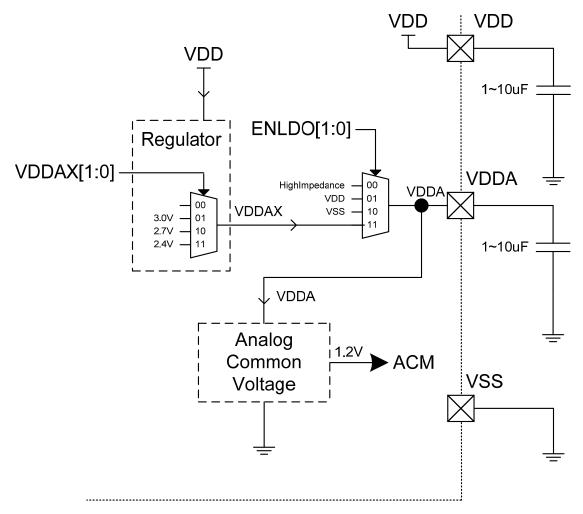

| 10.1.        | VDDA Manual                                   | 79  |

| 10.2.        | ACM Manual                                    | 79  |

| 10.3.        | Register Instruction-PWR                      | 79  |

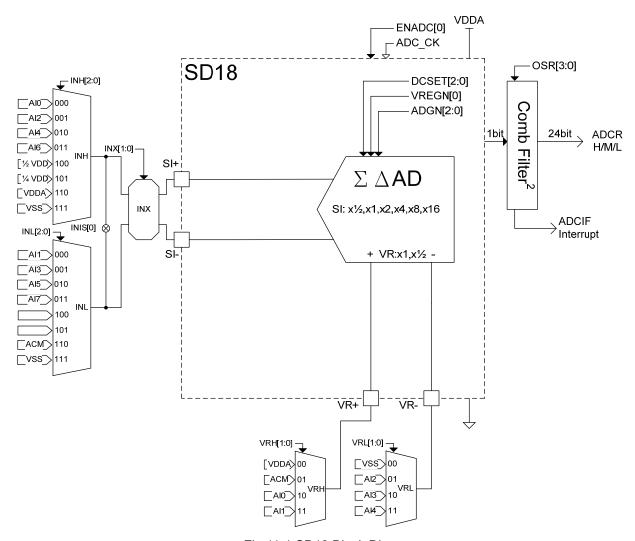

| 11. <i>A</i> | ANALOG DIGITAL CONVERTER SD18,ΣΔADC           | 80  |

| 11.1.        | SD18 Manual                                   | 82  |

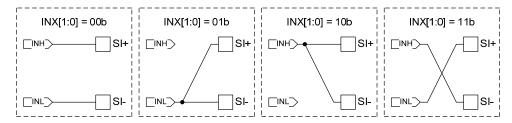

| 11.2.        | Analog Channel Input Features                 | 88  |

| 11.3.        | Register Instruction-SD18                     | 90  |

| 12. E        | BIE AND 16-BIT HARDWARE DATA RECORDER         | 94  |

| 12.1.        | BIE Manual:                                   | 95  |

| 12.2.        | Hardware Data Recorder                        | 97  |

| 12.3.        | Register Instruction-BIE                      | 98  |

| 13. (        | COMMUNICATION INTERFACE (CI)                  | 99  |

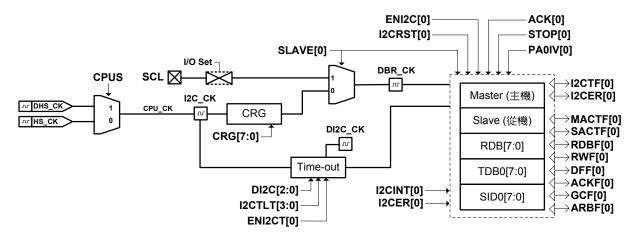

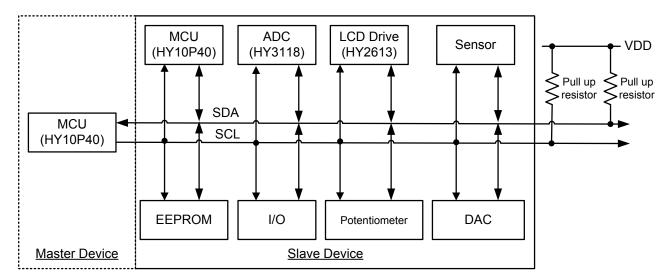

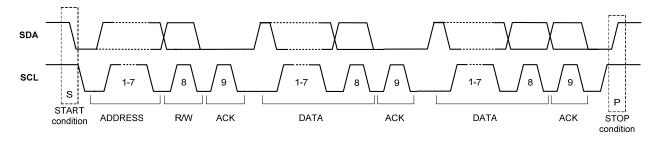

| 13.1.        | I2C Inter-Integrated Circuit Serial interface | 99  |

| 13.2.        | Data Transmission Ratio Calculation           | 101 |

### Embedded 18-Bit ΣΔΑDC 8-Bit RISC-like Mixed Signal Microcontroller

| 44 5  | AEVICION RECORD                              | 440 |

|-------|----------------------------------------------|-----|

| 13.5. | I2C Register Instructions                    | 108 |

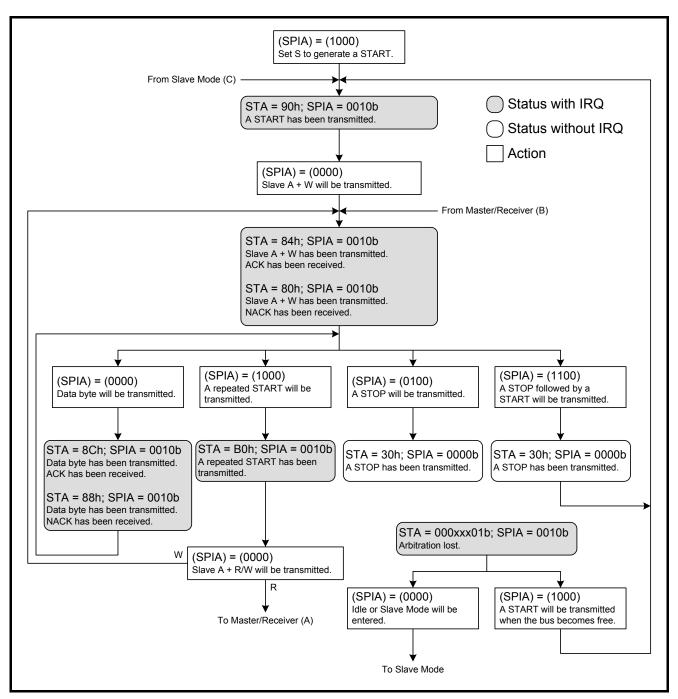

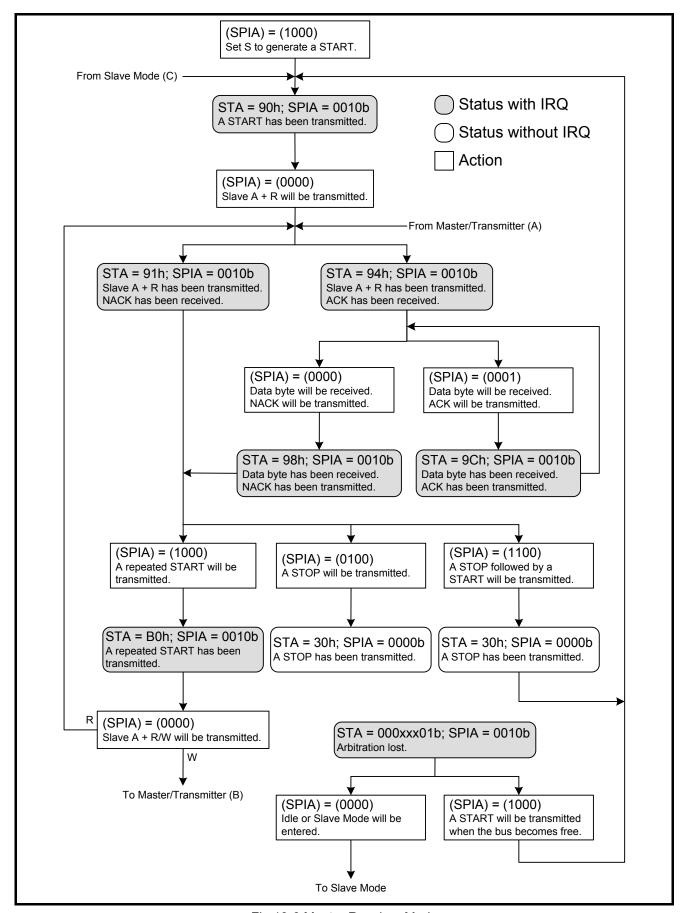

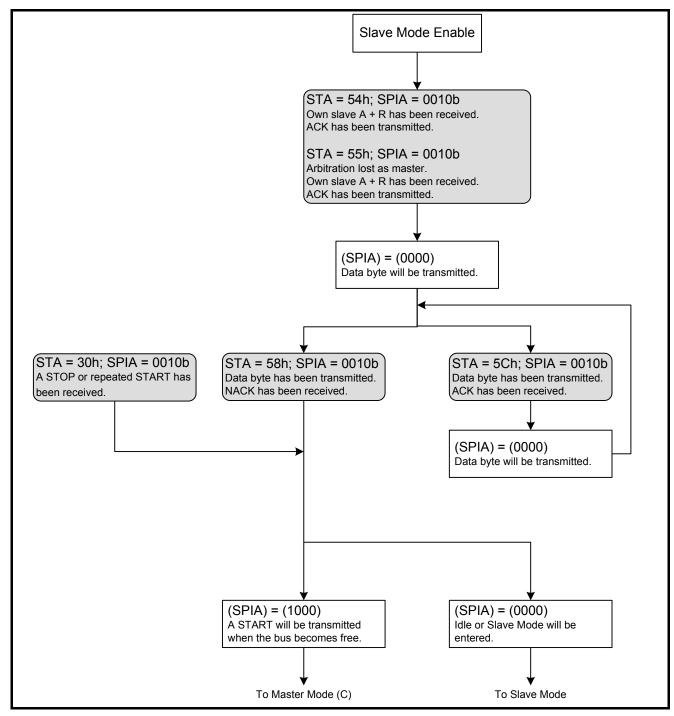

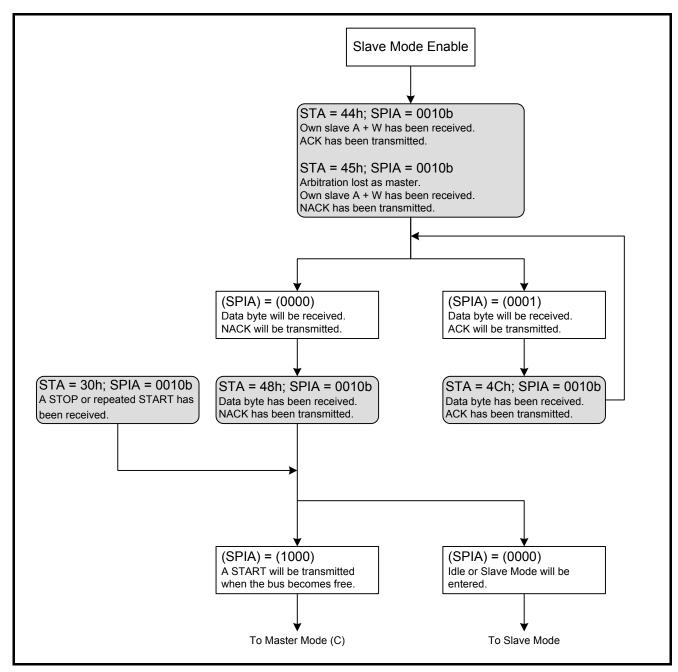

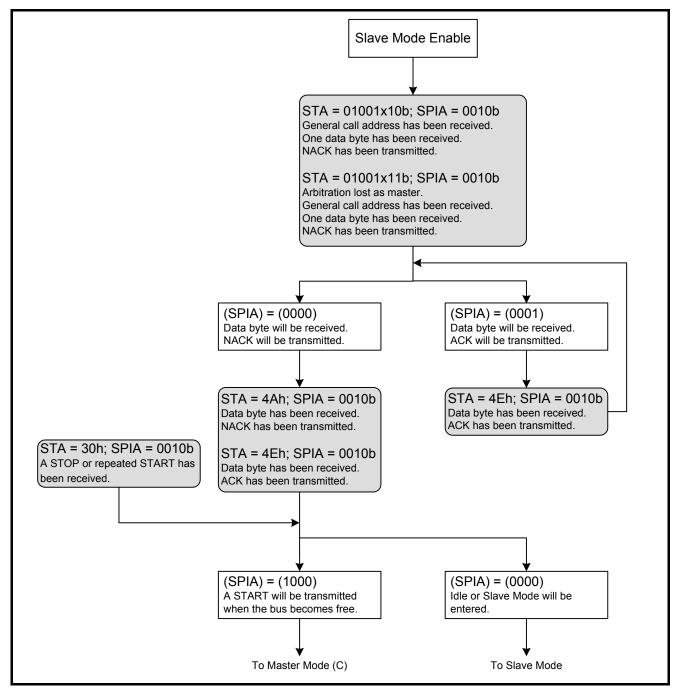

| 13.4. | I2C Serial Interface Communication Flowchart | 102 |

| 13.3. | Time-Out Function                            | 101 |

Embedded 18-Bit ΣΔADC 8-Bit RISC-like Mixed Signal Microcontroller

### 1. Reading Guidance

#### Attention:

- 1. HYCON Technology Corp. reserves the right to change the content of this datasheet without further notice. For most up-to-date information, please constantly visit our website: <a href="http://www.hycontek.com">http://www.hycontek.com</a>.

- 2. HYCON Technology Corp. is not responsible for problems caused by figures or application circuits narrated herein whose related industrial properties belong to third parties.

- 3. Specifications of any HYCON Technology Corp. products detailed or contained herein stipulate the performance, characteristics, and functions of the specified products in the independent state. We does not guarantee of the performance, characteristics, and functions of the specified products as placed in the customer's products or equipment. Constant and sufficient verification and evaluation is highly advised.

- 4. Please note the operating conditions of input voltage, output voltage and load current and ensure the IC internal power consumption does not exceed that of package tolerance. HYCON Technology Corp. assumes no responsibility for equipment failures that resulted from using products at values that exceed, even momentarily, rated values listed in products specifications of HYCON products specified herein.

- 5. Notwithstanding this product has built-in ESD protection circuit, please do not exert excessive static electricity to protection circuit.

- 6. Products specified or contained herein cannot be employed in applications which require extremely high levels of reliability, such as device or equipment affecting the human body, health/medical equipments, security systems, or any apparatus installed in aircrafts and other vehicles.

- 7. Despite the fact that HYCON Technology Corp. endeavors to enhance product quality as well as reliability in every possible way, failure or malfunction of semiconductor products may happen. Hence, users are strongly recommended to comply with safety design including redundancy and fire-precaution equipments to prevent any accidents and fires that may follow.

- 8. Use of the information described herein for other purposes and/or reproduction or copying without the permission of HYCON Technology Corp. is strictly prohibited.

### Embedded 18-Bit ΣΔADC 8-Bit RISC-like Mixed Signal Microcontroller

#### 1.1. Terms and Definition

### 1.1.1. Glossary

1MW 1MegaWord1KB 1KiloByte

ADC Analog to Digital Converter

Bit bit

BOR Brown-Out Reset

BSR Bank Select Register

Byte Byte

CCP Capture and Compare

CPU Central Processing Unit

DAC Digital-to-Analog Converter

DM Data Memory

ECAP Enhance Comparator FSR File Select Register

GPR General Purpose Register

HAO High Accuracy Oscillator

LNOP Low Noise OP AMP

LPO Low Power Oscillator

LSB Least Significant Bit

MEM Memory

MPM Main Program Memory

MSB Most Significant Bit

OTP One Time Program-EPROM

PC Program Counter

PPF PWM and PFD

SD18 Sigma-Delta ADC

SR Special Register

SRAM Static Random Access Memory

STK Stack

WDT Watch Dog Timer WREG Work Register

# Embedded 18-Bit ΣΔADC

8-Bit RISC-like Mixed Signal Microcontroller

### 1.1.2. Register Related Glossary

Register length []

< > Register value

ABC[7:0] ABC register had 0 to 7bit

ABC<111> ABC register had 3bit and value

had 111 of binary

ABC<11x> x : can be neglected, it can be set

as 1 or 0

Read/Write rw

Read only r0 Read as 0

Read as 1 r1

Write only w

Write as 0 w0

Write as 1 w1

h0 cleared by Hardware

set by Hardware h1

u0 cleared by User

u1 set by User

Not use

users are forbidden to change

unchanged u

unknown Χ

d depends on condition

Embedded 18-Bit ΣΔADC 8-Bit RISC-like Mixed Signal Microcontroller

### 2. Central Processing Unit (CPU)

#### 2.1. CPU Core

To get higher efficiency, CPU Core (H08) is adopted Harvard architecture concept. It separates the program memory and data memory respectively. Furthermore, the address of program memory increases the convenience of program writing for user.

#### CPU Features include:

- Separate design structures of program memory and data memory increase the instruction execution speed and improve the CPU efficiency.

- Max addressing capabilities are 1MW for program memory and 4096KB for data memory respectively.

- Max 46 operation instructions include block switching and stacking control of data memory.

- ◆ One instruction can complete data moving of FSR register with max 16-bit and address table look-up instruction of 1MW program memory.

- ◆ The operation of data memory includes the data moving of program counter (PC), status register (Status) and stack register (Stack).

- ◆ The CPU core is H08B core of starter edition.

Embedded 18-Bit ΣΔADC 8-Bit RISC-like Mixed Signal Microcontroller

### 2.2. Memory

The structure of memory has two types. One is program memory, which is composed of OTP, and the other is data memory, which is composed of SRAM. On different model product, planned memory size is also different. Therefore, it must pay special attention on specification of the product when reading the operation manual.

**Program Memory:**

Main Program Memory (MPM)

Program Counter (PC)

Stack (STK)

Data Memory:

Special Register (SR)

General Purpose Register (GPR)

**Related Register Abstract of Memory:** (x: means it is composed of multiple registers.)

**PC[10:0]** PCHSR[2:0],PCLATH[2:0],PCLATL[7:0]

**TOS[10:0]** TOSH[2:0],TOSL[7:0]

FSR0[7:0]

FSR0L[7:0]

INDF0

INDF0[7:0]

POINC0

POINC0[7:0]

PODEC0

PODEC0[7:0]

PRINC0

PRINC0[7:0]

PLUSW0

PLUSW0[7:0]

STKCN STKFL[0],STKOV[0],STKUN[0],STKPRT[2:0]

**PSTATUS** SKERR[0]

### 2.2.1. Program Memory

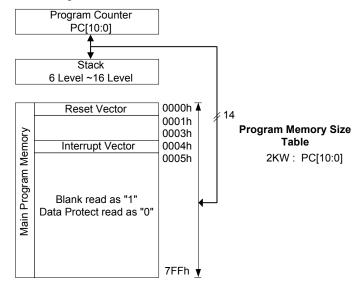

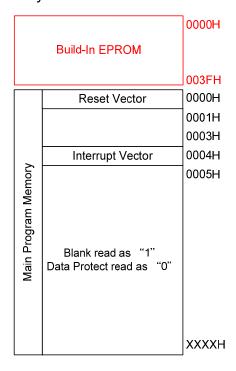

Fig 2-1 Program Memory Architecture

### 2.2.1.1. Main Program Memory (MPM)

### Main Program Memory Architecture is as the following:

- ◆ Interrupt Vector Position

- Reset Vector Position

Addressing capability is from 0x00000h to 0x7FFh, with a total capacity of 2048 Word.

When the chip is not taken program writing, data type of all addresses is 1. After writing, the addresses will be 1 or 0 according to the written data type. Note: in program development, if the assemble option of simulation software (HYIDE) has burn protection function setting, the data type of chip is 0 at the addresses that burning can be read.

### 2.2.1.2. Program Counter (PC)

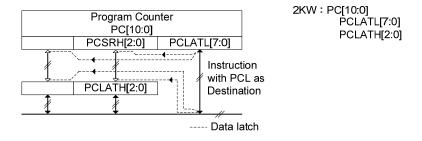

Program Counter (PC) is composed of shift register PCSR and buffer register PCLAT. See Fig 2-2.

Fig 2-2 PC Architecture

Embedded 18-Bit ΣΔADC 8-Bit RISC-like Mixed Signal Microcontroller

Chip used in tool development of PC [10:0] has 11-bit data length. It is composed of two special registers, PCSRH [2:0] and PCLATL [7:0]. PCLATL [7:0] and PCLATH [2:0] can be read / written directly, while PCSRH [2:0] cannot be read / written directly and it must use buffer register PCLATH [2:0] as indirect reading /writing.

- Before reading PC [10:0], it must read PCLATL [7:0] first and then read PCLATH [2:0] before reading correct data. Reverse order will not read correct data.

- Before writing PC [10:0], it must write PCLATH [2:0] and then PCLATL [7:0] finally.

Reverse order will not write correct data.

Embedded 18-Bit ΣΔADC 8-Bit RISC-like Mixed Signal Microcontroller

#### 2.2.1.3. Stack (STK)

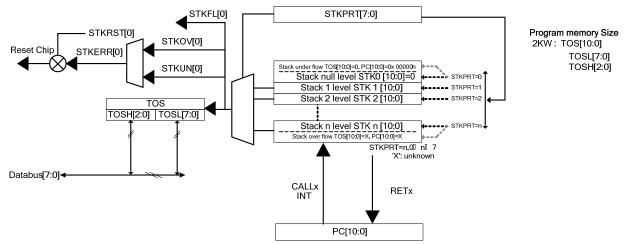

Stack (STK) is mainly composed of stack pointer control register STKCN, top stack register TOS0, stack layer register STKn<sup>1</sup>, stack error flag SKERR(Stack Error) and stack error reset controller SKRST[0], as in Fig 2-3.

Fig 2-3 Stack Architecture

Top stack register TOS [10:0] has 11-bit data length. It is composed of two registers, TOSH [2:0] and TOSL [7:0]. When STKPRT [2:0] =<0>, TOS [10:0] =<0> is null. When the program executes CALL instruction or appears interrupt (INT) service, stack pointer STKPRT [2:0] makes plus one motion and writes PC address when the event appears into TOS [10:0] register of the time. When the program executes RETx instruction, stack pointer STKPRT [2:0] makes minus one motion. Before taking minus one motion, it will write TOS [10:0] data in PC [10:0] in advance. After writing is completed, STKPRT [2:0] makes minus one motion and changes the current TOS [10:0] value.

- It has no special rules for TOS [10:0] register reading and can be read directly.

- TOS[10:0] register writhing can use CALL instruction or interrupt (INT) to write PC[10:0] data, or uses POP instruction to discard current TOS[10:0] data and make STKPRT[2:0]minus one and load new TOS[10:0] data.

During stack operation process, it may appear Stack full STKFL [0], Stack overflow STKOV [0] or Stack underflow STKUN[0] and other events. Stack full is an indication flag before Stack overflow. At the moment, it can discard current TOS [10:0] and make STKPRT [2:0] minus one and write stack layer data with new pointer in TOS [10:0] via POP instruction execution. Note: when STKPRT [2:0]=<0>, POP instruction execution will not appear underflow condition. At the moment, STKPRT [2:0] is still <0>. Therefore, the user must judge whether it is empty stack by oneself.

Stack layer register STKn: Each layer of stack has data register with the same length of top stack register TOS. When the stack pointer STKPRT is appointed, the content of data register is sent to TOS.

### Embedded 18-Bit ΣΔADC 8-Bit RISC-like Mixed Signal Microcontroller

When the stack appears overflow and underflow, it may lead to unexpected execution results for program. When necessary, it can restart chip via setting. In program development process, it can set stack reset control bit SKRST [0]<sup>2</sup> as <1> via software setting. When stack appears underflow or overflow, it may generate reset signal and shall restart chip after the SKERR [0] is set as <1>.

- Stack full: When STKFL [0] is set as <1>, PC[10:0] is not affected.

- Stack underflow: When STKUN[0] is set as <1>, PC[10:0] is moved to 0x00000hposition and stack pointer STKPRT points to 0 Level. If SKRST [0] is set as <1>, it may generate reset signal after stack underflow, and SKERR [0] is set as <1>. STKUN [0] is set as <0> after reset.

- Stack overflow: When STKOV[0] is set as <1>, PC[10:0] is not affected and STKPRT is still stopped at the final layer and it will press new value, i.e. it may reserve the last one pressing data after stack full. If SKRST[0] is set as <1>, it may generate reset signal after stack overflow, and SKERR [0] is set as <1>. STKOV[0] is set as <0> after reset.

- Error: When SKERR[0] is set as <1>, chip appears stack error. If SKRST[0] is set as <1>, STKUN[0] and STKOV[0] are set as <0> after reset.

- When it appears stack full, if it appears overflow condition as ignorance and continues executing POP instruction as ignorance and causes underflow condition, STKFL[0], STKOV[0] and STKOV[0] are set as <1> simultaneously. Therefore, it is suggested to make cleaning action for flags to avoid erroneous judgment of program when any one of above conditions appears.

If programming method has omitted the known overflow condition, it is suggested to use POP instruction to clear overflow flag and continue executing program after overflow appears. Otherwise, Interrupt or Call instruction generated stack writing motion after overflow will overlay current TOS[10:0] data.

© 2013 HYCON Technology Corp Preliminary UG-HY10S40-V03 EN Page 13

<sup>&</sup>lt;sup>2</sup> SKRST[0] is stack error generated reset signal control bit. It cannot be read /written directly and can only be set via software development at the program development stage, i.e. it must select whether it generates reset signal when stack error appears at the program development stage. If reset is selected, the bit is set as 1 after powering on the chip. Otherwise, it is set as <0>.

### Embedded 18-Bit ΣΔADC

8-Bit RISC-like Mixed Signal Microcontroller

### 2.2.1.4. Register Instruction---Program Memory Controller

|         | "-"no use,"*"read/write,"w"write,"r"read,"r0"only read 0,"r1"only read 1,"w0"only write 0,"w1"only write 1 |       |                                  |       |       |       |         |           |        |             |             |

|---------|------------------------------------------------------------------------------------------------------------|-------|----------------------------------|-------|-------|-------|---------|-----------|--------|-------------|-------------|

|         | "\$"for event status,"."unimplemented bit,"x"unknown,"u"unchanged,"d"depends on condition                  |       |                                  |       |       |       |         |           |        |             |             |

| Address | Name                                                                                                       | Bit 7 | Bit 6                            | Bit 5 | Bit 4 | Bit 3 | Bit 2   | Bit 1     | Bit 0  | ARST        | IRST        |

| 016h    | TOSH                                                                                                       | -     | -                                | -     | -     | -     | TOS[10] | TOS[9]    | TOS[8] | xxxx        | uuuu        |

| 017h    | TOSL                                                                                                       |       | Top-of-Stack Low Byte (TOS<7:0>) |       |       |       |         |           |        | XXXX XXXX   | uuuu uuuu   |

| 018h    | SKCN                                                                                                       | SKFL  | SKUN                             | SKOV  | -     | -     |         | SKPRT[2:0 | ]      | 000000      | u\$\$\$\$\$ |

| 01Ah    | PCLATH                                                                                                     | -     | -                                | -     | -     | -     | PC[10]  | PC[9]     | PC[8]  | 0000        | 0000        |

| 01Bh    | PCLATL                                                                                                     |       | PC Low Byte for PC<7:0>          |       |       |       |         |           |        | 0000 0000   | 0000 0000   |

| 02Ch    | PSTATUS                                                                                                    | POR   | PD                               | TO    | IDL   | RST   | SKERR   | -         | -      | \$000 \$00. | uu\$u u\$u. |

Table 2-1 Program Memory Control Register

TOSU/TOSH/TOSL: Stacked Top Stack Register

TOSH: TOS[10:8] TOSL: TOS[7:0]

STKPTR: Stack Controller

STKFL: Stack Full Flag

1: Occurred

0: Not Occurred

STKUN: Stack Underflow Flag

1: Occurred

0: Not Occurred

STKOV: Stack Overflow Flag

1: Occurred

0: Not Occurred

STKPRT[2:0]: Stack Pointer Register

111: 7<sup>th</sup> layer 110: 6<sup>th</sup> layer

00000: 0 layer TOS[10:0]=0x0000h

PCLATU/PCLATH/PCLATL: Program Counter PC[10:0]

PCLATH: PC[10:8] PCLATL: PC[7:0]

**PSTATUS: Status Register**

SKERR: Stack Error Generated Reset Flag

1: Occurred

0: Not Occurred

Embedded 18-Bit ΣΔADC 8-Bit RISC-like Mixed Signal Microcontroller

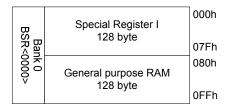

### 2.2.2. Data Memory (DM)

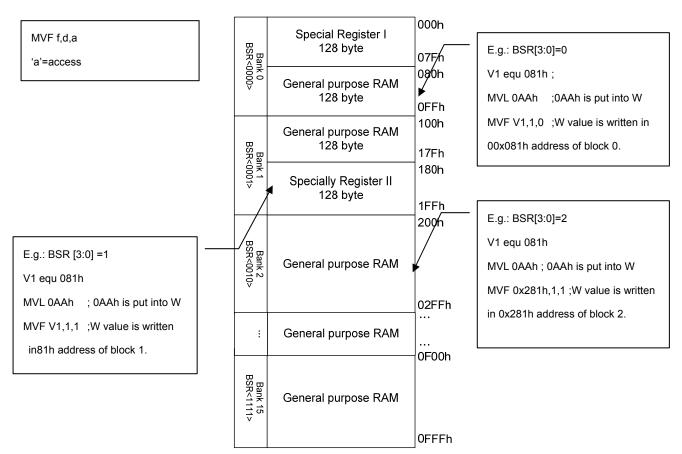

Data Memory (DM) is composed of Specially Register (SR) and General Purpose Register (GPR). Furthermore, it takes every 256byte as a block. 128byte Specially Register and 128 byte General Purpose Register is as in Fig 2-4.

Fig 2-4 Data Memory (DM) Architecture

### 2.2.2.1. Memory and Instruction

H08 instruction set can be divided A and B two version, which have great difference in memory application, such as addressing capability, hardware multiplier, table look-up instruction, support functions and parameters definition. Here just illustrate definition of instruction memory parameters. See Instruction part of Instruction Set on detailed instruction parameter illustration.

Instructions with address computation function in instruction set have three parameters at most, i.e. "f", "d" and "a".

- "f" refers to Data or Data Memory Address.

- "d" refers to data storage place after computation. If d=0, it is stored in WREG register. If d=1, it is stored in Data Memory Register.

- "a" is memory operation block appointing. If a=0, it is operated in block 0. If a=1, it is operated in BSR [3:0] appointed block.

Embedded 18-Bit ΣΔADC 8-Bit RISC-like Mixed Signal Microcontroller

### 2.2.2.2. Block Selection Control Register

Data memory is planned every 256byte as a block, i.e. 000h~0FFh is a block. If it is going to read / write data register after 0FFh address, it shall set block control register BSR [3:0] and instruction parameter "a" correctly. It is illustrated as the following:

- ◆ When a = 0, no matter BSR[3:0] is appointed at any block, the reading / writing of instruction to memory can only be at block 0.

- When a = 1, the reading / writing of H08A CPU Core instruction to data memory will be at BSR [3:0] appointed block. The reading / writing of H08B CPU Core instruction to data memory will be at block 0.

Example 2-1 Relation between Block Selector Example Program and Data Memory

Embedded 18-Bit ΣΔADC 8-Bit RISC-like Mixed Signal Microcontroller

### 2.2.2.3. Special Register (SR)

Special Register (SR) includes CPU Core peripheral function related registers. It mainly has control function register and data return register. If it takes reading for address which is not defined in data register or address used bit, read data is 0.

In SR, it also has several registers dedicated in instruction collocation. It just introduces two kinds of commonly used registers. One is working register WREG and the other is indirect addressing register FSR. The rest special registers, which are not introduced here, will be taken detailed illustration in each chapter.

### 2.2.2.3.1. Working Register (WREG)

Working register is shortened as W. It is the most frequently used register for instruction collocation, ranging from data movement, computation and judgment etc.

Embedded 18-Bit ΣΔADC 8-Bit RISC-like Mixed Signal Microcontroller

### 2.2.2.3.2. Indirect Addressing Register, FSR and INDF

FSR indirect addressing register is composed of index register FSR0[9:0] and index registers INDF0[7:0] and INDF1[7:0]. As the functions are similar, it just illustrates FSR0.

FSR0L [7:0] can write 16-bit data by using an instruction via a special instruction.

INDF0 [7:0] is index register and it can read the data of FSRL0 [7:0] pointed data memory address. Functions are described as the following:

- ◆ POINC0[7:0]: When read /write POINC0[7:0] register via instruction, the following events may appear:

- Return the contents of current FSR0 [7:0] pointed address firstly.

- The value of index register FSR0 [7:0] is added one and pointed to next address.

- PODEC0[7:0]: When read /write PODEC0[7:0] register via instruction, the following events may appear:

- Return the contents of current FSR0 [7:0] pointed address firstly.

- The value of index register FSR0 [7:0] is minus one and pointed to previous address.

- PRINC0[7:0]: When read /write POINC0[7:0] register via instruction, the following events may appear:

- The value of index register FSR0 [7:0] is added one and pointed to next address firstly.

- Return the contents of current FSR0 [7:0] pointed address then.

- ▶ PLUSW0 [7:0]: When read /write PLUSW0 [7:0] register via instruction, the following events may appear:

- Add the value of index register FSR0 [7:0] to the content of working register W firstly.

- Return contents of current FSR0 [7:0] pointed address. W content is values with sign bit, i.e. ±128d.

### 2.2.2.3.3. General Purpose Register (GPR)

General Purpose Register (GPR) takes data storage, computation, flag setting and other free planning area for the users.

Embedded 18-Bit ΣΔADC 8-Bit RISC-like Mixed Signal Microcontroller

### 2.2.2.4. Register Instruction---Data Memory Controller

|         | "-"no use,"*"read/write,"w"write,"r"read,"r0"only read 0,"r1"only read 1,"w0"only write 0,"w1"only write 1 |       |                                                                       |           |               |               |              |            |       |           |           |

|---------|------------------------------------------------------------------------------------------------------------|-------|-----------------------------------------------------------------------|-----------|---------------|---------------|--------------|------------|-------|-----------|-----------|

|         | "\$"for event status,"."unimplemented bit,"x"unknown,"u"unchanged,"d"depends on condition                  |       |                                                                       |           |               |               |              |            |       |           |           |

| Address | Name                                                                                                       | Bit 7 | Bit 6                                                                 | Bit 5     | Bit 4         | Bit 3         | Bit 2        | Bit 1      | Bit 0 | ARST      | IRST      |

| 000h    | INDF0                                                                                                      |       | Contents of FSR0 to address data memoryvalue of FSR0 not changed      |           |               |               |              |            |       |           | uuuu uuuu |

| 001h    | POINC0                                                                                                     |       | Contents of FSR0 to address data memoryvalue of FSR0 post-incremented |           |               |               |              |            |       |           | uuuu uuuu |

| 002h    | PODEC0                                                                                                     |       | Contents of F                                                         | SR0 to ad | dress data me | moryvalue of  | FSR0 post-de | ecremented |       | XXXX XXXX | uuuu uuuu |

| 003h    | PRINC0                                                                                                     |       | Contents of F                                                         | SR0 to ac | ddress data m | emoryvalue of | FSR0 pre-in  | cremented  |       | XXXX XXXX | uuuu uuuu |

| 004h    | PLUSW0                                                                                                     |       | Contents of FSR0 to address data memoryvalue of FSR0 offset by W      |           |               |               |              |            |       | xxxx xxxx | uuuu uuuu |

| 010H    | FSR0L                                                                                                      |       | Indirect Data Memory Address Pointer 0 Low Byte,FSR0[7:0]             |           |               |               |              |            |       | xxxx xxxx | uuuu uuuu |

| 029h    | WREG                                                                                                       |       |                                                                       |           | Working       | Register      |              |            |       | XXXX XXXX | uuuu uuuu |

Table 2-2 Data Memory Control Register

#### INDF0/POINC0/PODEC0/PRINC0/PLUSW0: Index register with different functions

INDF0[7:0]: .See 2.2.2.3.2 Indirect Addressing Register, FSR and INDF Description in detail.

POINC0[7:0]: See 2.2.2.3.2 Indirect Addressing Register, FSR and INDF Description in detail.

PODEC0[7:0]: See 2.2.2.3.2 Indirect Addressing Register, FSR and INDF Description in detail.

PRINC0[7:0]: See 2.2.2.3.2 Indirect Addressing Register, FSR and INDF Description in detail.

PLUSW0[7:0]: See 2.2.2.3.2 Indirect Addressing Register, FSR and INDF Description in detail.

#### FSR0: Indirectly Addresses Index Register

FSR0L[7:0]: See 2.2.2.3.2 Indirect Addressing Register, FSR and INDF Description in detail.

#### WREG: Indirectly Addresses Index Register

WREG[7:0]: See 2.2.2.3.1 Working Register, WREG Description in detail.

Embedded 18-Bit ΣΔADC 8-Bit RISC-like Mixed Signal Microcontroller

### 2.2.3. Register List-Data Memory

| only write 1 | write 0,"w1" | i 1,"w0"only v                   | 1"only read                       | nly read 0,"ı  | r"read,"r0"o    | ite,"w"write," | *"read/wr   | "-"no use,"   |       |         |         |

|--------------|--------------|----------------------------------|-----------------------------------|----------------|-----------------|----------------|-------------|---------------|-------|---------|---------|

| n condition  | d"depends o  | unchanged,"d                     | known,"u"ı                        | ed bit,"x"un   | unimplement     | ent status,"." | "\$"for eve |               |       |         |         |

| IRST         | ARST         | Bit 0                            | Bit 1                             | Bit 2          | Bit 3           | Bit 4          | Bit 5       | Bit 6         | Bit 7 | Name    | Address |

| uuuu uuuu    | xxxx xxxx    |                                  | changed                           | of FSR0 not    | nemoryvalue     | address data ı | f FSR0 to a | Contents o    |       | INDF0   | 000h    |

| uuuu uuuu    | xxxx xxxx    |                                  | cremented                         | FSR0 post-ir   | moryvalue of    | dress data me  | SR0 to add  | Contents of F |       | POINC0  | 001h    |

| uuuu uuuu    | xxxx xxxx    |                                  | ecremented                        | SR0 post-de    | moryvalue of l  | lress data me  | SR0 to add  | Contents of F |       | PODEC0  | 002h    |

| uuuu uuuu    | xxxx xxxx    |                                  | cremented                         | FSR0 pre-in    | moryvalue of    | dress data me  | SR0 to ad   | Contents of F |       | PRINC0  | 003h    |

| uuuu uuuu    | xxxx xxxx    |                                  | et by W                           | of FSR0 offs   | memoryvalue     | address data   | of FSR0 to  | Contents      |       | PLUSW0  | 004h    |

| uuuu uuuu    | xxxx xxxx    |                                  | 7:0]                              | v Byte,FSR0[   | Pointer 0 Lov   | mory Address   | ct Data Me  | Indired       |       | FSR0L   | 010H    |

| uuuu         | xxxx         | TOS[8]                           | TOS[9]                            | TOS[10]        | -               | -              | -           | -             | -     | TOSH    | 016h    |

| uuuu uuuu    | XXXX XXXX    | Top-of-Stack Low Byte (TOS<7:0>) |                                   |                |                 |                |             |               |       | TOSL    | 017h    |

| u\$\$\$\$\$  | 000000       | )]                               | SKPRT[2:0                         |                | -               | =              | SKOV        | SKUN          | SKFL  | STKPTR  | 018h    |

| 0000         | 0000         | PC[8]                            | PC[9]                             | PC[10]         | -               | -              | -           | -             | -     | PCLATH  | 01Ah    |

| 0000 0000    | 0000 0000    |                                  |                                   |                | for PC<7:0>     | PC Low Byte    |             |               |       | PCLATL  | 01Bh    |

| Ouuu uuuu    | 0000 0000    | E0IE                             | -                                 | TMAIE          | TB1IE           | WDTIE          | -           | ADIE          | GIE   | INTE1   | 023h    |

| uuuu uuuu    | 0000 0000    | -                                | -                                 | I2CIE          | I2CERIE         | =              | -           | -             | -     | INTE2   | 024h    |

| .uuu uuuu    | .000 0000    | E0IF                             | -                                 | TMAIF          | TB1IF           | WDTIF          | -           | ADIF          | -     | INTF1   | 026h    |

| uuuu uuuu    | 0000 0000    | -                                | -                                 | I2CIF          | I2CERIF         | -              | -           | -             | -     | INTF2   | 027h    |

| uuuu uuuu    | xxxx xxxx    |                                  | Working Register                  |                |                 |                |             |               |       | WREG    | 029h    |

| u uuuu       | x xxxx       | Z                                | -                                 | -              | -               | С              | -           | -             | -     | STATUS  | 02Bh    |

| uu\$u u\$u.  | \$000 \$00.  | -                                | -                                 | SKERR          | RST             | IDL            | TO          | PD            | BOR   | PSTATUS | 02Ch    |

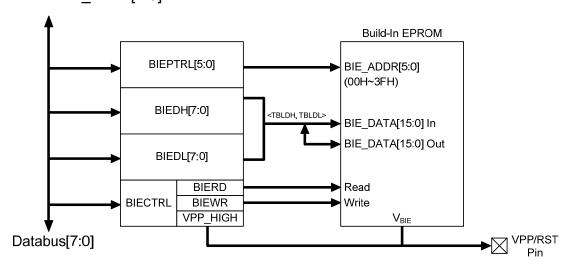

| 1 \$.uu      | 1 \$.00      | BIERD                            | BIEWR                             | -              | VPPHV           | -              | -           | -             | -     | BIECN   | 02Eh    |

| u uuuu       | 0 xxxx       | BIEAH[2:0]                       | -up Table as                      | 11-bit look    | -               | -              | -           | -             | ENBIE | BIEARH  | 02Fh    |

| uuuu uuuu    | xxxx xxxx    |                                  | BIEAL[7:0]                        | up Table as I  | or 11-bit look- | s BIEAL[5:0]   | Register a  | BIE Address   |       | BIEARL  | 030h    |

| uuuu uuuu    | xxxx xxxx    |                                  |                                   | r              | Data Registe    | BIE High Byte  | E           |               |       | BIEDRH  | 031h    |

| uuuu uuuu    | xxxx xxxx    |                                  |                                   |                | Data Register   | BIE Low Byte   |             |               |       | BIEDRL  | 032h    |

| uuuu u00u    | 0000 0000    | CSFON                            | ADRST                             | -              | -               | AX[1:0]        | VDD         | OO[1:0]       | ENLD  | PWRCN   | 033h    |

| uuuu uuuu    | 0000 0000    | CPUS                             |                                   | DMS[2:0]       |                 | IS[1:0]        | DH          | S[1:0]        | OSC   | OSCCN0  | 034h    |

| uuuu uuu.    | 0000 0000    | TMBS                             | 3[1:0]                            | DTMI           |                 | ADCS[2:0]      |             | -             | -     | OSCCN1  | 035h    |

| .uuu uu11    | .000 0011    | LPO                              | ENHAO                             | <b>/</b> [1:0] | HAON            | -              | -           | -             | -     | OSCCN2  | 036h    |

| uuuu \$000   | 0000 0000    | ]                                | DWDT[2:0]                         |                | ENWDT           | -              |             | -             | -     | WDTCN   | 037h    |

| u0uu uu      | 0000 00      | -                                | -                                 |                | DTMA[2:0]       |                | TMAS        | TMACL         | ENTMA | TMACN   | 038h    |

| uuuu uuuu    | 0000 0000    |                                  |                                   |                | er Register     | TMA count      |             |               |       | TMAR    | 039h    |

| u.uu uuuu    | 0.10 0000    |                                  | SKRST EN_RST_PIN HAOTR[5:0]       |                |                 |                |             |               |       | CSFCN0  | 041h    |

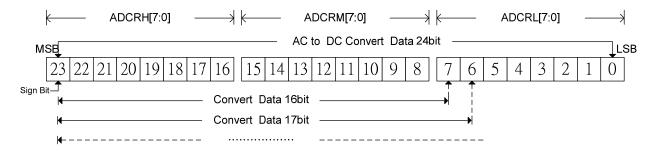

| uuuu uuuu    | xxxx xxxx    |                                  | ADC conversion memory HighByte    |                |                 |                |             |               |       | ADCRH   | 043h    |

| uuuu uuuu    | xxxx xxxx    |                                  | ADC conversion memory Middle Byte |                |                 |                |             |               |       | ADCRM   | 044h    |

| uuuu uuuu    | xxxx xxxx    |                                  | ADC conversion memory Low Byte    |                |                 |                |             |               |       | ADCRL   | 045h    |

| 0000 0000    | 0000 0000    | ]                                | ADGN[2:0]                         |                | -               | -              | ENCHP       | ENHIGN        | ENADC | ADCCN1  | 046h    |

| 0000         | 0000         | )]                               | DCSET[2:0                         |                | VREGN           | -              | -           | -             | -     | ADCCN2  | 047h    |

| 0000.        | 0000.        | -                                | -                                 | -              | -               |                | :0]         | OSR[3         |       | ADCCN3  | 048h    |

Table 2-3 Data Memory List

### Embedded 18-Bit ΣΔΑDC 8-Bit RISC-like Mixed Signal Microcontroller

|             |         |       | "-"no use,                    | ""read/wr  | ite,"w"write,  | ʻr"read,"r0"o   | only read 0," | r1"only reac | d 1,"w0"only | write 0,"w1" | only write 1 |

|-------------|---------|-------|-------------------------------|------------|----------------|-----------------|---------------|--------------|--------------|--------------|--------------|

|             |         |       |                               | "\$"for ev | ent status,"." | unimplement     | ted bit,"x"ur | ıknown,"u"ı  | unchanged,"d | d"depends o  | n condition  |

| Address     | Name    | Bit 7 | Bit 6                         | Bit 5      | Bit 4          | Bit 3           | Bit 2         | Bit 1        | Bit 0        | ARST         | IRST         |

| 049h        | AINET1  |       | INH[2:0]                      |            |                | INL[2:0]        |               | INIS         | -            | 0000 000.    | 0000 000.    |

| 04Ah        | AINET2  | -     | VRH[1                         | :0]        | INX            | [1:0]           | VRL           | [1:0]        | -            | .000 000.    | .000 000.    |

| 04Eh        | TB1Flag | -     | -                             | PWM6A      | PWM5A          | PWM4A           | PWM3A         | PWM2A        | PWM1A        | 00 0000      | uu uuuu      |

| 04Fh        | TB1CN0  | ENTB1 | TB1M[1:0]                     |            | TB1R           | T[1:0]          | TB1CL         | -            | -            | 0000 0000    | uuuu u0uu    |

| 050h        | TB1CN1  | PA1IV | V PWMA1[2:0] PA0IV PWMA0[2:0] |            |                |                 |               |              | 0000 0000    | uuuu uuuu    |              |

| 051h        | TB1RH   |       |                               | Ti         | merB1 counte   | r Register [15  | :8]           |              |              | xxxx xxxx    | uuuu uuuu    |

| 052h        | TB1RL   |       |                               | Т          | imerB1 counte  | er Register [7: | 0]            |              |              | xxxx xxxx    | uuuu uuuu    |

| 053h        | TB1C0H  |       |                               | TimerB     | 1 counter Cor  | dition Registe  | er [15:8]     |              |              | xxxx xxxx    | uuuu uuuu    |

| 054h        | TB1C0L  |       |                               | Timer      | 31 counter Co  | ndition Regist  | er [7:0]      |              |              | XXXX XXXX    | uuuu uuuu    |

| 055h        | TB1C1H  |       |                               | TimerB     | 1 counter Cor  | dition Registe  | er [15:8]     |              |              | xxxx xxxx    | uuuu uuuu    |

| 056h        | TB1C1L  |       |                               | Timer      | 31 counter Co  | ndition Regist  | er [7:0]      |              |              | XXXX XXXX    | uuuu uuuu    |

| 057h        | TB1C2H  |       |                               | TimerB     | 1 counter Cor  | dition Registe  | er [15:8]     |              |              | XXXX XXXX    | uuuu uuuu    |

| 058h        | TB1C2L  |       |                               | Timer      | 31 counter Co  | ndition Regist  | er [7:0]      |              |              | xxxx xxxx    | uuuu uuuu    |

| 061h        | CFG     |       |                               | Rsv.       |                |                 | I2CRST        | ENI2CT       | ENI2C        | 000          | uuu          |

| 062h        | ACT     | SLAVE | -                             | -          | I2CER          | START           | STOP          | I2CINT       | ACK          | 0000 0000    | uuuu uuuu    |

| 063h        | STA     | MACTF | SACTF                         | RDBF       | RWF            | DFF             | ACKF          | GCF          | ARBF         | 0001 0000    | uuuu uuuu    |

| 064h        | CRG     |       |                               |            | CRG            | [7:0]           |               |              |              | 0000 0000    | uuuu uuuu    |

| 065h        | TOC     | I2CTF |                               | DI2C[2:0]  |                |                 | I2CTL         | T[3:0]       |              | 0000 0000    | uuuu uuuu    |

| 066h        | RDB     |       |                               |            | RDB[7:1]       |                 |               |              | RDB[0]       | xxxx xxxx    | uuuu uuuu    |

| 067h        | TDB0    |       |                               |            | TDB0[7:1]      |                 |               |              | TDB[0]       | xxxx xxxx    | uuuu uuuu    |

| 068h        | SID0    |       | SID[7:1],T                    | he corresp | onding addre   | ss of the 7-bit | mode          |              | SIDV[0]      | 0000 0000    | uuuu uuuu    |

| 070h        | PT1     | -     | -                             | -          | -              | -               | -             | -            | PT10         | xxxx         | xxxx         |

| 071h        | TRISC1  | -     | -                             | -          | -              | -               | -             | =            | -            | 0000 0000    | uuuu uuuu    |

| 072h        | PT1DA   | -     | -                             | -          | -              | -               | -             | -            | -            | 0000 0000    | uuuu uuuu    |

| 073h        | PT1PU   | -     | -                             | -          | -              | -               | -             | -            | -            | 0000 0000    | uuuu uuuu    |

| 074h        | PT1EG   | -     | -                             | FPWMA1     | FPWMA0         | -               | -             | E0E          | G[1:0]       | 0000         | uuuu         |

| 075h        | PT2     | -     | -                             | -          | -              | -               | -             | PT21         | PT20         | xx           | xx           |

| 076h        | TRISC2  | -     | -                             | -          | -              | -               | -             | TC21         | TC20         | 00           | uu           |

| 077h        | PT2DA   | -     | -                             | -          | -              | -               | -             | DA21         | DA20         | 00           | uu           |

| 078h        | PT2PU   | -     | -                             | -          | -              | -               | -             | PU21         | PU20         | 00           | uu           |

| 079h        | PT3     | -     | -                             | PT35       | PT34           | PT33            | PT32          | PT31         | PT30         | xx xxxx      | xx xxxx      |

| 07Ah        | TRISC3  | -     | -                             | TC35       | TC34           | TC33            | TC32          | TC31         | TC30         | 00 0000      | uu uuuu      |

| 07Bh        | PT3DA   | -     | -                             | DA35       | DA34           | DA33            | DA32          | DA31         | DA30         | 00 0000      | uu uuuu      |

| 07Ch        | PT3PU   | -     | -                             | PU35       | PU34           | PU33            | PU32          | PU31         | PU30         | 00 0000      | uu uuuu      |

| 080h ~ 0FFh | GPR0    |       |                               | Gene       | eral Purpose R | legister as 12  | 8Byte         |              |              | uuuu uuuu    | uuuu uuuu    |

Table 2-4 Data Memory List (Continued)

Embedded 18-Bit ΣΔADC 8-Bit RISC-like Mixed Signal Microcontroller

### 3. Oscillator, Clock Source and Power Consumption Management

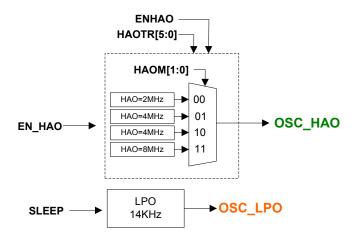

HY10P Series have two clock sources, ie HAO and LPO, as in Table 3-1. It can distribute and manage CPU and peripheral working frequency feasibly through clock controller register. Furthermore, it can adjust power consumption of chip properly to reach the energy saving purpose.

### **Abstract of Clock Control Register:**

OSCCN0 OSCS[1:0],DHS[1:0],DMS[2:0],CPUS[0] LCPS[1:0],ADCS[2:0],DTMB[1:0],TMBS[0] OSCCN1

OSCCN2 HAOM[1:0], ENHAO[0], LPO[0]

| Sign | Frequency | Frequ         | uency Contr   | oller       | Instructio  | n Execution Status |

|------|-----------|---------------|---------------|-------------|-------------|--------------------|

|      |           | OSCCN         | 2[7:0] Config | guration    |             |                    |

|      |           | ENHAO[0]      | HAOM[1]       | SLP         | IDLE        |                    |

| HAO  | 8MHz      | 1             | 1             | 1           | Stop        | Oscillation        |

|      | 4MHz      | 1             | 0             | 1           | Stop        | Oscillation        |

|      | 2MHz      | 1             | 0             | Stop        | Oscillation |                    |

| LPO  | 14KHz     | Oscillation i | s started aft | er the chip | Stop        | Oscillation        |

|      |           | į:            | s power on.   |             |             |                    |

Table 3-1 Internal RC Oscillator Parameter, Frequency Controller Configuration and Instruction Status

#### 3.1. Oscillator

#### 3.1.1. HAO Oscillator

HAO is internal high speed RC oscillator. Typical output frequency is 2.0~8.0MHz. When CPU of HY10P series products uses other oscillators as working clock source, it can shut off the HAO oscillator via ENHAO[0] setting.

#### 3.1.2. LPO Oscillator

LPO is internal low speed RC oscillator. Typical output frequency is 14KHz. As the current consumption of LPO is about 0.7uA, it is mainly applied to low speed and power saving CPU working mode and Watch Dog Timer clock source.

After HY10P series of products execute Sleep instructions, LPO oscillator is shut off. LPO will be started oscillation automatically when the chip is awakened.

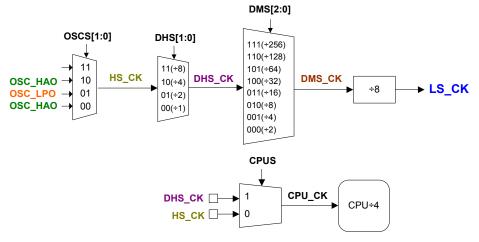

### 3.2. CPU and Peripheral Circuit Clock Source

### 3.2.1. Clock Source Configuration

Two groups of oscillators output (OSC\_HAO \ OSC\_LPO) will be started /stopped, switched and pre-scaled frequency via pre-set working clock distributor, and then enter CPU and all peripheral circuits of chip, as in Fig 3-1.

Fig 3-1 Pre-set Working Clock Distributor

#### 3.2.2. CPU Clock Source

CPU has several working frequency for option. Via CPUS [0], optional working frequency is from HS CK or DHS CK.

Instruction working frequency adopts 1/4 CPU\_CK design and frequency is divided to frequency source of INTR\_CK.

- When operating ΣΔADC, it is suggested to divide current working frequency after using HS CK for CPU to obtain better performance.

- When CPU\_CK frequency and instruction execute cycle, it is as in Fig 3-2. Table 3-2 lists the relation between CPU working frequency and instruction cycle briefly.

Fig 3-2 CPU and Peripheral Working Clock

Embedded 18-Bit ΣΔΑDC 8-Bit RISC-like Mixed Signal Microcontroller

| Working Freque | CPU       | Instruction |         |  |  |

|----------------|-----------|-------------|---------|--|--|

| ncy<br>CPU_CK  | Frequency | Frequency   | Cycle   |  |  |

| 8MHZ           | 8MHZ      | 2MHz        | 0.5us   |  |  |

| 4MHz           | 4MHz      | 1MHz        | 1us     |  |  |

| 2MHz           | 2MHz      | 500kHz      | 2us     |  |  |

| 14KHz          | 14KHz     | 3.5KHz      | 285.7us |  |  |

Table 3-2 CPU Working Frequency and Instruction Execution Cycle

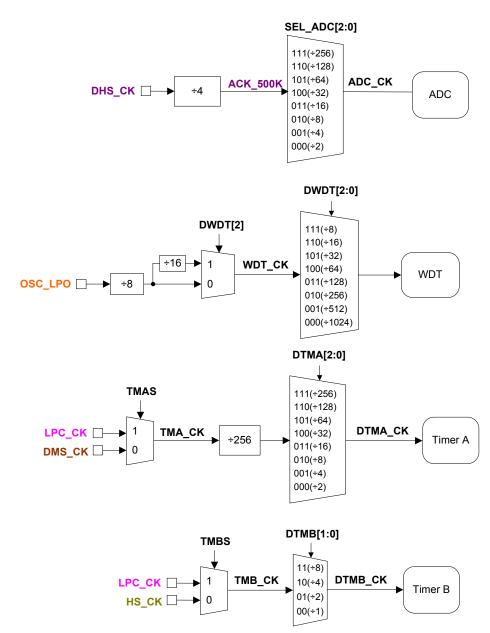

### 3.2.3. CPU Peripheral Circuit Clock Source

Working clock of HY10P series peripheral circuits is configured by different configuration controller and frequency pre-scaler. The configuration will make detailed illustration in peripheral units, so peripheral working clock configuration diagram is just attached here, as in Fig 3-3.

Fig 3-3 Peripheral Working Clock Configuration Diagram

Embedded 18-Bit ΣΔADC 8-Bit RISC-like Mixed Signal Microcontroller

### 3.3. Register Instruction-Working Clock Source Controller

|         | "-"no use,"*"read/write,"w"write,"r"read,"r0"only read 0,"r1"only read 1,"w0"only write 0,"w1"only write 1 |       |                 |       |           |       |         |           |           |           |           |

|---------|------------------------------------------------------------------------------------------------------------|-------|-----------------|-------|-----------|-------|---------|-----------|-----------|-----------|-----------|

|         | "\$"for event status,"."unimplemented bit,"x"unknown,"u"unchanged,"d"depends on condition                  |       |                 |       |           |       |         |           |           |           |           |

| Address | Name                                                                                                       | Bit 7 | Bit 6           | Bit 5 | Bit 4     | Bit 3 | Bit 2   | Bit 1     | Bit 0     | ARST      | IRST      |

| 033h    | PWRCN                                                                                                      |       |                 |       |           |       |         |           | CSFON     | 0000 0000 | uuuu u00u |

| 034h    | OSCCN0                                                                                                     | OSC   | S[1:0] DHS[1:0] |       | DMS[2:0]  |       | CPUS    | 0000 0000 | uuuu uuuu |           |           |

| 035h    | OSCCN1                                                                                                     | -     | -               |       | ADCS[2:0] | ]     | DTMI    | B[1:0]    | TMBS      | 0000 0000 | uuuu uuu. |

| 036h    | OSCCN2                                                                                                     | -     | -               | -     | -         | HAON  | Λ[1:0]  | ENHAO     | LPO       | .000 0011 | .uuu uu11 |

| 041h    | CSFCN0                                                                                                     | SKRST | EN_RST_PIN      |       |           | HAO   | TR[5:0] |           |           | 0.10 0000 | u.uu uuuu |

Table 3-3 Working Clock Source Control Register

### OSCCN0 [7:0] Chip Working Frequency Control Register 0

Frequency Controller of OSCS [1:0] HS\_CK

<11> Not Used

<10>OSC\_HAO

<01>OSC\_LPO

<00>OSC\_HAO

Frequency Allocation Selector of DHS [1:0] DHS\_CK

<11>HS\_CK ÷ 8

<10>HS\_CK ÷ 4

<01>HS\_CK ÷ 2

<00>HS\_CK ÷ 1

Frequency Allocation Selector of DMS [2:0] DMS\_CK

<111>DHS\_CK ÷ 256

<110>DHS\_CK ÷ 128

<101>DHS CK ÷ 64

<100>DHS\_CK ÷ 32

<011>DHS\_CK ÷ 16

<010>DHS\_CK ÷ 8

<001>DHS\_CK ÷ 4

<000>DHS\_CK ÷ 2

Frequency Selector of CPUS [0] CPU\_CK

<1>DHS\_CK

<0>HS\_CK

### Embedded 18-Bit ΣΔADC

8-Bit RISC-like Mixed Signal Microcontroller

### OSCCN1 [7:0] Chip Working Frequency Control Register 1

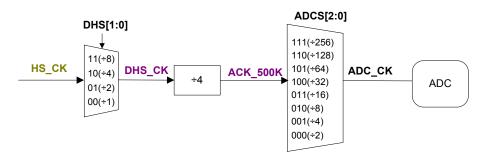

ADCS [2:0]: SD18 Peripheral Working Frequency Pre-eliminator

111: ADC\_CK/256

110: ADC\_CK/128

101: ADC\_CK/64

100: ADC\_CK/32

011: ADC\_CK/16

010: ADC\_CK/8

001: ADC\_CK/4

000: ADC CK/2

Frequency Allocation Selector of DTMB [1:0] DTMB\_CK

<11>TMB\_CK ÷ 8

<10>TMB\_CK ÷ 4

<01>TMB\_CK ÷ 2

<00>TMB CK ÷ 1

Frequency Selector of TMBS [0] TMB\_CK

<1>LPC\_CK

<0>HS\_CK

#### OSCCN2 [7:0] Chip Working Frequency Control Register 2

HAOM [1:0] Internal Oscillator HAO Oscillation Frequency Selector

<11>8MHz

<10> cannot be set

<01>4MHz

<00>2MHz

ENHAO: Internal HAO Start Control Bit

1: Start

0: Stop

LPO [0] Internal Oscillator LPO Status Flag

<1> Start

<0>Stop

\*The bit is status bit. It can only be read but not written. After executing Sleep instruction, LPO oscillator will be stopped automatically. When the chip is awakened, LPO will be started automatically.

### Embedded 18-Bit ΣΔADC 8-Bit RISC-like Mixed Signal Microcontroller

### PWRCN [7:0] Linear Regulator and Analog Control Register

CSFON [0] CSF (Chip Special Function) Start writing controller

<1> Start CSF writing function. When the user is necessary to set block control register, it must set the CFSON[0] as <1> before writing in CSFCN0[7:0].

<0> Not start CSF function.

### CSFCN0[7:0] Special Control Bit Register

### HAOTR[5:0]HAO Frequency Center Adjustment Controller

| <111111>Adjust -10%, minimum | <101001>Adjust -2.90%        | <010011>Adjust 4.06%           |

|------------------------------|------------------------------|--------------------------------|

| <111110>Adjust -9.68%        | <101000>Adjust -2.58%        | <010010>Adjust 4.38%           |

| <111101>Adjust -9.35%        | <100111>Adjust -2.26%        | <010001>Adjust 4.69%           |

| <111100>Adjust -9.03%        | <100110>Adjust -1.94%        | <010000>Adjust 5.00%           |

| <111011>Adjust -8.71%        | <100101>Adjust -1.61%        | <001111>Adjust 5.31%           |

| <111010>Adjust -8.39%        | <100100>Adjust -1.29%        | <001110>Adjust 5.63%           |

| <111001>Adjust -8.06%        | <100011>Adjust -0.97%        | <001101>Adjust 5.94%           |

| <111000>Adjust -7.74%        | <100010>Adjust -0.65%        | <001100>Adjust 6.25%           |

| <110111>Adjust -7.42%        | <100001>Adjust -0.32%        | <001011>Adjust 6.56%           |

| <110110>Adjust -7.10%        | <100000> Central point 0.00% | <001010>Adjust 6.88%           |

| <110101>Adjust -6.77%        | <011111>Adjust 0.31%         | <001001>Adjust 7.19%           |

| <110100>Adjust -6.45%        | <011110>Adjust 0.63%         | <001000>Adjust 7.50%           |

| <110011>Adjust -6.13%        | <011101>Adjust 0.94%         | <000111>Adjust 7.81%           |

| <110010>Adjust -5.81%        | <011100>Adjust 1.25%         | <000110>Adjust 8.13%           |

| <110001>Adjust -5.48%        | <011011>Adjust 1.56%         | <000101>Adjust 8.44%           |

| <110000>Adjust -5.16%        | <011010>Adjust 1.88%         | <000100>Adjust 8.75%           |

| <101111>Adjust -4.84%        | <011001>Adjust 2.19%         | <000011>Adjust 9.06%           |

| <101110>Adjust -4.52%        | <011000>Adjust 2.50%         | <000010>Adjust 9.38%           |

| <101101>Adjust -4.19%        | <010111>Adjust 2.81%         | <000001>Adjust 9.69%           |

| <101100>Adjust -3.87%        | <010110>Adjust 3.13%         | <000000>Adjust 10.00%, maximum |

| <101011>Adjust -3.55%        | <010101>Adjust 3.44%         |                                |

| <101010>Adjust -3.23%        | <010100>Adjust 3.75%         |                                |

|                              |                              |                                |

Embedded 18-Bit ΣΔADC 8-Bit RISC-like Mixed Signal Microcontroller

### 3.4. Power Consumption Management and Operation Status

HY10P series CPU provides three types of working modes to make user obtain best management on execution effectiveness and power saving. The three types of modes are operation mode, standby mode and sleep mode.

### 3.4.1. Operation Mode

Operation mode mainly refers to that CPU handles all appeared events according to clock source. At the moment, chip peripheral can be operated normally and power consumption handles max status under the same clock.

### 3.4.2. Standby Mode

Standby mode is entered via IDLE instruction. It mainly refers to that CPU stops operating waiting for wake when enter energy saving status, and sets IDLEB [0] flag bit of PSTATUS reset register as <1>. Under this mode, chip peripheral can be operated normally. When the peripheral appears interrupt event, it will awaken CPU<sup>3</sup>. Additionally, watch dog counter finally generated signal belongs to interrupt signal, but not reset signal.

Under standby mode, CPU is in pause mode and is stopped under the IDLE instruction. The internal oscillator is not affected and also is not closed. If the user wants to reach energy saving status, it depends on the application condition. At the moment, it shall switch off peripheral or oscillator and other resources. The chip must get to the standby mode status via external interrupt source or other peripheral resource interrupt signal.

Under standby mode, if it encounters interrupt resource and leaves standby mode, it needs 2 instruction cycles time to back to 04H position of interrupt vector. If the CPU frequency source is internal ideal 2MHZ, the other instruction cycle time is 2usec. Therefore, it needs 4usec program for awakening and to back to the position of interrupt vector. If CPU frequency source is internal ideal 14KHZ, the other instruction cycle time is 286usec. Therefore, it needs 536usec program for awakening and to back to the position of interrupt vector.

If under standby mode, CPU frequency source is internal 14KHZ, and internal 2MHZ oscillator has been closed, while 2MHZ oscillator is started after awakening, complete starting 2MHZ oscillator requires two 14KHZ instruction awakening time plus 128 2MHZ instruction oscillation time. It is equivalent to about 792usec. After it, internal 2MHZ oscillator can be completed oscillation normally.

<sup>&</sup>lt;sup>3</sup>After CPU is suffered interrupt signal awakening, PC (Program Counter) will jump to interrupt vector position (0x004h). See Reset and Interrupt Section on detailed illustration on PSTATUS reset register and interrupt service vector.

#### 4. RESET

HY10P series of reset circuits include the following 4 types of events to trigger reset signal. Reset block diagram is as Fig 4-1.

- **♦ BOR** power interference reset

- ◆ RST external reset input pin

- ◆ WDT watch dog reset

- ◆ **SKERR** stack error reset (determined by the user)

### **Abstract of Operation Status Register:**

**PSTATUS** BOR[0],PD[0],TO[0],IDL[0],SKERR[0]

Fig 4-1 Reset Block Diagram

These reset events can be divided into software reset and hardware reset, as in Table 4-1. CPU reset program is started by 0x0000h.

|   | Reset    | Event Sign |         | Description                                     |

|---|----------|------------|---------|-------------------------------------------------|

|   | Type     |            |         |                                                 |

|   | Hardware | BOR        |         | CPU restart needs internal oscillator           |

|   |          | RST        | A-RESET | completes counter starting before entering      |

|   | Reset    |            |         | normal operation status.                        |

| Ī | Software | WDT        | I-RESET | It only clears partial register. CPU is back to |

|   | Reset    | SKERR      | I-RESEI | normal operation status rapidly.                |

Table 4-1 Reset Rank List

### 4.1. Reset Event Description

#### 4.1.1. BOR Power Interference Reset

When CPU is suffered from external interference during powering on process or the power is suffered from external interference, CPU will enter into normal operation voltage from abnormal operation and low operation voltage. Therefore, if CPU cannot be in reset status

### Embedded 18-Bit ΣΔADC 8-Bit RISC-like Mixed Signal Microcontroller

when the operation voltage is too low, it may cause crash of CPU and make the operation of peripheral circuits abnormal. Therefore, it must rely on BOR circuit function. When it detects that operation voltage is suffered from interference and voltage level is lower than the designed value, it may generate reset signal and make chip enter restart status, until the operation voltage is recovered. Then it will relieve reset signal and make chip enter normal operation mode.

When BOR reset occurs, BOR[0] flag in PSTATUS[7:0] register is set as <1> to record the occurred event.

HY10P series of BOR circuits will generate about 0.6uA power consumption. It cannot be closed via program or other setting method.

### 4.1.2. RST External Input Reset

When the voltage level of external RST pin is lower than designed value<sup>4</sup>, it may generate reset signal and make chip enter restart status, until the operation voltage is recovered. Then it will relieve reset signal and make chip enter normal operation mode.

### 4.1.3. WDT Watch Dog Counter Reset

WDT watch dog counter may generate reset signal and make chip enter rapid start status when the operation mode counter is ended. When WDT watch dog occurs reset, TO[0] flag in the PSTATUS[7:0] register will be set as <1> to record the occurred event.

Note: WDT watch dog finally generated signal has two types. It may generate reset signal when the chip is under operation mode. If the chip is under standby mode, it may generate interrupt event signal to awaken CPU. See *Watch DOG WDT Section* on detailed operation description.

### 4.1.4. SKERR Stack Error Reset

When the program occurs stack overflow or underflow, it may generate reset signal and make chip enter rapid start status. When SKERR stack error reset occurs, SKERR[0] flag in PSTATUS[7:0] register is set as <1> to record the occurred event. See *Memory Section* on detailed operation description.

<sup>&</sup>lt;sup>4</sup> The pin has another two kinds of functions. One is when RST input voltage is pulled up to meet  $V_{IU}$  specification, the chip enters OTP program mode. The other is when RST input voltage meets  $V_{IL}$  specification, the chip enters current leakage test mode.

Embedded 18-Bit ΣΔADC 8-Bit RISC-like Mixed Signal Microcontroller

### 4.2. Status Register

Chip operation status is displayed in PSTATUS[7:0] reset register. Mutual relation is as in Table 4-2.

"0": Not Occured, "1": Occurred, "u": Not Changed, "-": Not Used

| Name /Status   | Address | 7   | 6  | 5  | 4   | 3  | 2     | 1 | 0 |

|----------------|---------|-----|----|----|-----|----|-------|---|---|

| PSTATUS        | 02CH    | BOR | PD | TO | IDL | ST | SKERR | ı | - |

| Hardware Reset | BOR     | 1   | 0  | 0  | 0   | 0  | 0     | - | - |

| (A-RESET)      | RST     | 0   | 0  | 0  | 0   | 1  | 0     | ı | - |

| Software Reset | WDT     | u   | u  | 1  | u   | u  | u     | - | - |

| (I-RESET)      | SKERR   | u   | u  | u  | u   | u  | 1     | - | - |

Table 4-2 Reset Status Flags Relation Table

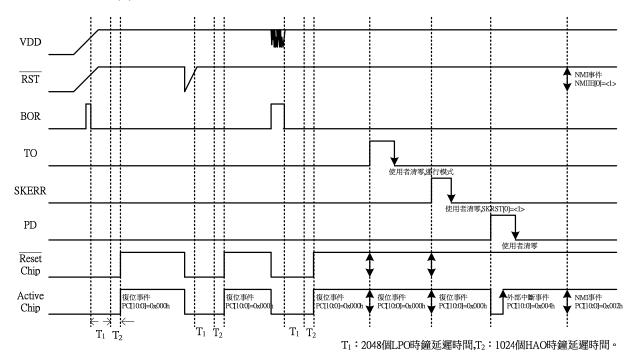

### 4.2.1. Sequence Diagram of Reset Status

Sequence diagram from hardware reset signal occurrence to entering operation status is as in Fig 4-2. Time from different reset signal occurrence to entering operation status is as in Table 3-2(b).

Fig 4-2 Sequence Diagram of Reset & Operation Mode and Status Flags

### 4.2.2. Register Instruction---Reset Status

| "-"no use,"*"read/write,"w"write,"r"read,"r0"only read 0,"r1"only read 1,"w0"only write 0,"w1"only write 1 |                                                                                          |       |            |            |       |        |        |        |       |             |             |

|------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------|-------|------------|------------|-------|--------|--------|--------|-------|-------------|-------------|

|                                                                                                            | "\$"for event status,"."unimplemented bit,"x"unknown,"u"unchanged,"d"depends on conditio |       |            |            |       |        |        |        |       |             |             |

| Address                                                                                                    | Name                                                                                     | Bit 7 | Bit 6      | Bit 5      | Bit 4 | Bit 3  | Bit 2  | Bit 1  | Bit 0 | ARST        | IRST        |

| 02Ch                                                                                                       | PSTATUS                                                                                  | BOR   | PD         | TO         | IDL   | RST    | SKERR  | -      | -     | \$000 \$00. | uu\$u u\$u. |

| 033h                                                                                                       | PWRCN                                                                                    | ENLO  | OO[1:0]    | VDDAX[1:0] |       | ENREFO | AD1RST | AD2RST | CSFON | 0000 0000   | uuuu u00u   |

| 041h                                                                                                       | CSFCN0                                                                                   | SKRST | EN_RST_PIN |            |       |        |        |        |       | 0.10 0000   | u.uu uuuu   |

Table 4-3 Reset Register

#### **PSTATUS: Status Register**

BOR[0]: BOR reset event flag

<1>Power interference reset has been occurred. It shall use RST or instruction for clearing.

<0>Not occurred interference reset

PD[0] : SLEEP event flag

<1>Sleep event has been occurred. It shall use BOR, RST or instruction for clearing.

<0> Not occurred sleep event

TO[0]: WDT operation mode counting overflow flag

<1> WDT reset event has been occurred. It shall use BOR, RST or instruction for clearing.

<0> Not occurred WDT counting overflow event

IDL [0] : Standby IDLE event flag

<1> IDLE event has been occurred. It shall use BOR, RST or instruction for clearing.

<0> Not occurred IDLE event

RST[0] ; External RST pin low potential event flag

<1> RST pin reset event has been occurred. It shall use BOR, or instruction for clearing.

<0> Not occurred RST pin reset event

SKERR[0] : Stack error reset flag

<1> Stack error. It shall use BOR, RST or instruction for clearing.

<0> No stack error

#### PWRCN[7:0] Linear Regulator and Analog Control Register

CSFON [0] CSF (Chip Special Function) Start writing controller

<1> Start CSF writing function. When the user is necessary to set block control register, it must set the CFSON[0] as <1> before writing in CSFCN0[7:0].

<0> Not start CSF function. CSFCN0[7:0] register cannot be read / written.

#### CSFCN0[7:0] Special Control Bit Register

SKRST[0] Stack error reset controller

<1> Start error reset chip

<0> Not start error reset chip

EN\_RST\_PIN[0] Reset chip pin set

<1>Not start hardware reset chip pin, set PT1.0 as general input.

<0> Start hardware reset chip pin. PT1.0 is set as RST pin.

Embedded 18-Bit ΣΔADC 8-Bit RISC-like Mixed Signal Microcontroller

### 4.3. Register List-Data Memory Reset Status

| "-"no use,"*"read/write,"w"write,"r"read,"r0"only read 0,"r1"only read 1,"w0"only write 0,"w1"only wr |         |                                   |             |            |                |                 |              |               |              |             | only write 1 |

|-------------------------------------------------------------------------------------------------------|---------|-----------------------------------|-------------|------------|----------------|-----------------|--------------|---------------|--------------|-------------|--------------|

|                                                                                                       |         |                                   |             | "\$"for ev | ent status,"." | unimplement     | ed bit,"x"ur | ıknown,"u"ı   | unchanged,"d | d"depends o | n condition  |

| Address                                                                                               | Name    | Bit 7                             | Bit 6       | Bit 5      | Bit 4          | Bit 3           | Bit 2        | Bit 1         | Bit 0        | ARST        | IRST         |

| 000h                                                                                                  | INDF0   |                                   | xxxx xxxx   | uuuu uuuu  |                |                 |              |               |              |             |              |

| 001h                                                                                                  | POINC0  |                                   | xxxx xxxx   | uuuu uuuu  |                |                 |              |               |              |             |              |

| 002h                                                                                                  | PODEC0  |                                   | xxxx xxxx   | uuuu uuuu  |                |                 |              |               |              |             |              |

| 003h                                                                                                  | PRINC0  |                                   | xxxx xxxx   | uuuu uuuu  |                |                 |              |               |              |             |              |

| 004h                                                                                                  | PLUSW0  |                                   | xxxx xxxx   | uuuu uuuu  |                |                 |              |               |              |             |              |

| 010H                                                                                                  | FSR0L   |                                   | xxxx xxxx   | uuuu uuuu  |                |                 |              |               |              |             |              |

| 016h                                                                                                  | TOSH    | -                                 | -           | -          | -              | -               | TOS[10]      | TOS[9]        | TOS[8]       | xxxx        | uuuu         |

| 017h                                                                                                  | TOSL    |                                   |             | Тор        | o-of-Stack Low | Byte (TOS<7     | :0>)         |               |              | xxxx xxxx   | uuuu uuuu    |

| 018h                                                                                                  | STKPTR  | SKFL                              | SKUN        | SKOV       | -              | -               |              | SKPRT[2:0     | ]            | 000000      | u\$\$\$\$\$  |

| 01Ah                                                                                                  | PCLATH  | -                                 | -           | -          | -              | -               | PC[10]       | PC[9]         | PC[8]        | 0000        | 0000         |

| 01Bh                                                                                                  | PCLATL  |                                   | •           | •          | PC Low Byte    | e for PC<7:0>   | -            | •             | -            | 0000 0000   | 0000 0000    |

| 023h                                                                                                  | INTE1   | GIE                               | ADIE        | -          | WDTIE          | TB1IE           | TMAIE        | -             | E0IE         | 0000 0000   | Ouuu uuuu    |

| 024h                                                                                                  | INTE2   | -                                 | -           | -          | -              | I2CERIE         | I2CIE        | -             | -            | 0000 0000   | uuuu uuuu    |

| 026h                                                                                                  | INTF1   | -                                 | ADIF        | -          | WDTIF          | TB1IF           | TMAIF        | -             | E0IF         | .000 0000   | .uuu uuuu    |

| 027h                                                                                                  | INTF2   | -                                 | -           | -          | -              | I2CERIF         | I2CIF        | -             | -            | 0000 0000   | uuuu uuuu    |

| 029h                                                                                                  | WREG    |                                   |             |            | Working        | Register        |              |               |              | xxxx xxxx   | uuuu uuuu    |

| 02Bh                                                                                                  | STATUS  | -                                 | -           | -          | С              | -               | -            | -             | Z            | x xxxx      | u uuuu       |

| 02Ch                                                                                                  | PSTATUS | BOR                               | PD          | то         | IDL            | RST             | SKERR        | -             | -            | \$000 \$00. | uu\$u u\$u.  |

| 02Eh                                                                                                  | BIECN   | -                                 | -           | -          | -              | VPPHV           | -            | BIEWR         | BIERD        | 1 \$.00     | 1 \$.uu      |

| 02Fh                                                                                                  | BIEARH  | ENBIE                             | -           | -          | -              | -               | 11-bit lool  | r-up Table as | 0 xxxx       | u uuuu      |              |

| 030h                                                                                                  | BIEARL  |                                   | BIE Address | Register a | as BIEAL[5:0]  | or 11-bit look- | up Table as  | BIEAL[7:0]    |              | xxxx xxxx   | uuuu uuuu    |

| 031h                                                                                                  | BIEDRH  |                                   |             |            | BIE High Byte  | Data Registe    | r            |               |              | xxxx xxxx   | uuuu uuuu    |

| 032h                                                                                                  | BIEDRL  |                                   |             |            | BIE Low Byte   | Data Register   | r            |               |              | xxxx xxxx   | uuuu uuuu    |

| 033h                                                                                                  | PWRCN   | ENL                               | DO[1:0]     | VDE        | DAX[1:0]       | -               | -            | ADRST         | CSFON        | 0000 0000   | uuuu u00u    |

| 034h                                                                                                  | OSCCN0  | OSC                               | S[1:0]      | DH         | HS[1:0]        |                 | DMS[2:0]     | <u> </u>      | CPUS         | 0000 0000   | uuuu uuuu    |

| 035h                                                                                                  | OSCCN1  | -                                 | -           |            | ADCS[2:0       | ]               | DTM          | B[1:0]        | TMBS         | 0000 0000   | uuuu uuu.    |

| 036h                                                                                                  | OSCCN2  | -                                 | -           | -          | -              | HAON            | И[1:0]       | ENHAO         | LPO          | .000 0011   | .uuu uu11    |

| 037h                                                                                                  | WDTCN   | -                                 | -           |            | _              | ENWDT DWDT[2:0] |              | 0000 0000     | uuuu \$000   |             |              |