# HY16F3981

## 用戶手冊

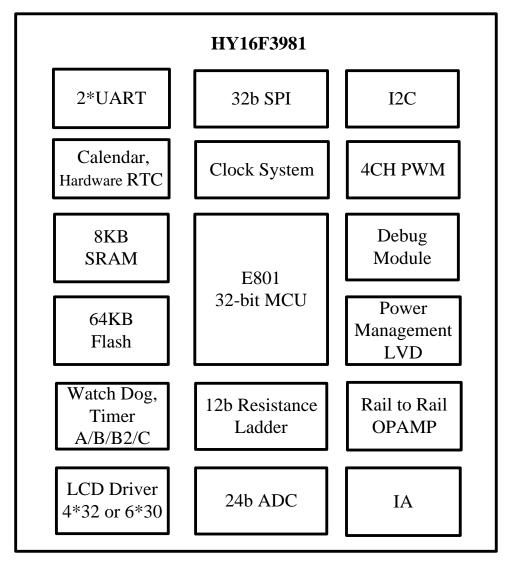

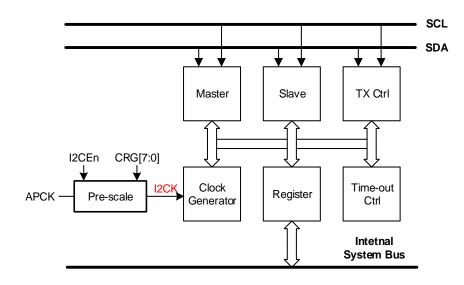

高精密混合信號處理控制器 4x32 ~ 6x30 LCD Driver 32-bit 低功耗微控制器 21-bit ENOB ΣΔADC 64KB Flash ROM

## HY16F3981 User's Guide 21-bit ENOB ΣΔΑDC, 32-bit MCU & 64KB Flash 4×32~6×30 LCD Driver

## 目錄

| 1.   | 晶片概述             | 10 |

|------|------------------|----|

| 1.1. | 簡介               | 10 |

| 1.2. | 型態說明表            | 11 |

| 2.   | 功能概述             | 12 |

| 2.1. | 方塊圖              | 12 |

| 2.2. | 中央處理器核心方框圖       | 13 |

| 3.   | 記憶體結構            | 14 |

| 3.1. | 記憶體說明            | 14 |

| 3.2. | 記憶體位址            | 15 |

| 3.3. | 靜態隨機存取記憶體(SRAM)  | 16 |

| 3.4. | 快閃記憶體(Flash ROM) | 16 |

| 3.5. | 匯流排介面單元          | 17 |

| 3.6. | 開機記憶體(Boot ROM)  | 18 |

| 3.7. | 嵌入式除錯模組(EDM)     | 18 |

| 4.   | <b>系統暫存器</b>     | 19 |

| 4.1. | 整體總說明            | 19 |

| 4.2. | 暫存器位址            | 19 |

| 4.3. | 暫存器功能            | 19 |

| 5.   | 電源管理             | 21 |

| 5.1. | 整體總說明            | 21 |

| 5.2. | 暫存器位址            | 25 |

## 21-bit ENOB ΣΔADC, 32-bit MCU & 64KB Flash

| 5.3.  | 暫存器功能        | 25 |

|-------|--------------|----|

| 6.    | 時脈系統         | 27 |

| 6.1.  | 整體總說明        | 27 |

| 6.2.  | 暫存器位址        | 31 |

| 6.3.  | 暫存器功能        | 31 |

| 7.    | 中斷控制系統       | 39 |

| 7.1.  | 整體總說明        | 39 |

| 7.2.  | 暫存器位址        | 40 |

| 7.3.  | 暫存器功能        | 40 |

| 8.    | 看門狗 WDT      | 52 |

| 8.1.  |              | 52 |

| 8.2.  | 暫存器位址        | 53 |

| 8.3.  |              | 53 |

| 9.    | 中味 STMFD A   | 55 |

|       |              |    |

| 9.1.  | 整體總說明        | 55 |

| 9.2.  | 暫存器位址        | 56 |

| 9.3.  | 暫存器功能        | 57 |

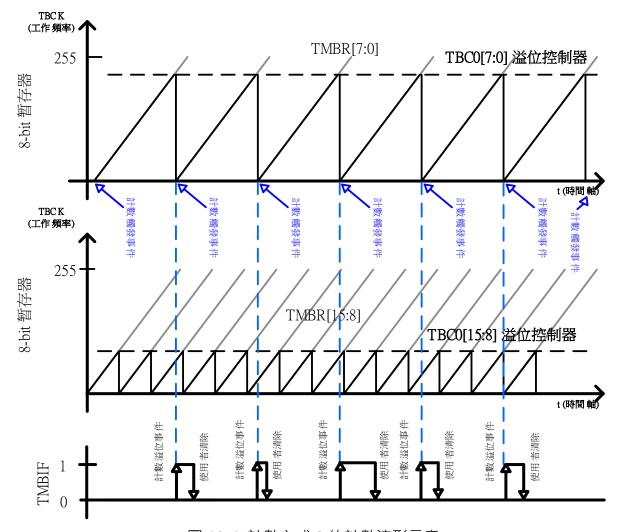

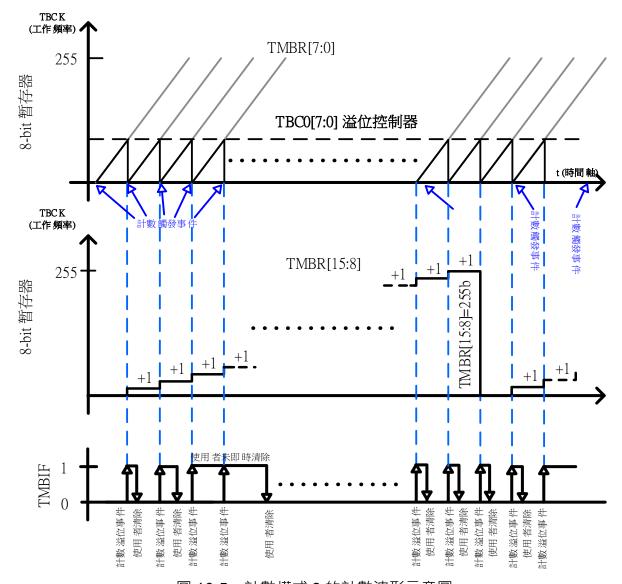

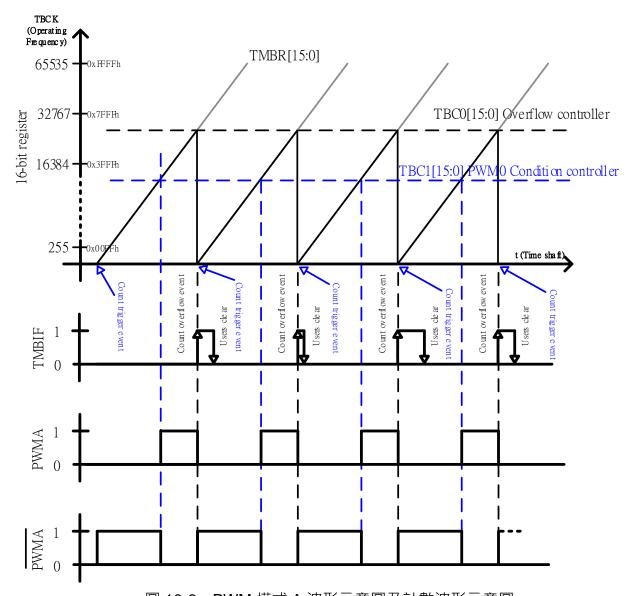

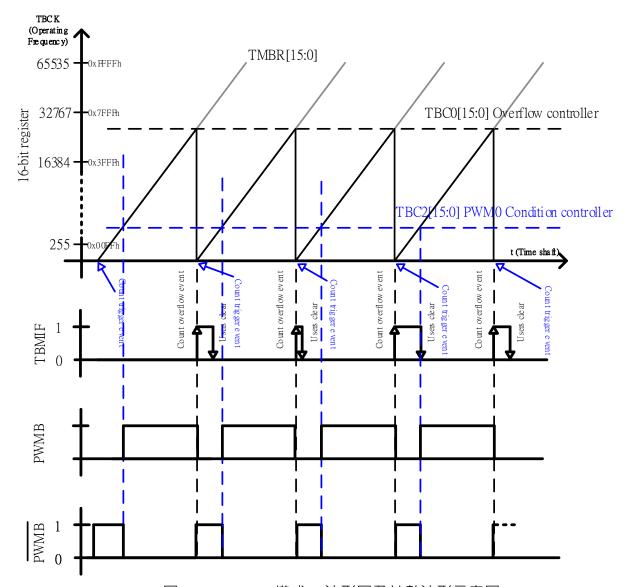

| 10.   | 定時器 TIMER B  | 58 |

| 10.1. | 整體總說明        | 58 |

| 10.2. | 暫存器位址        | 85 |

| 10.3. | 暫存器功能        | 85 |

| 11.   | 定時器 TIMER B2 | 88 |

## 21-bit ENOB ΣΔADC, 32-bit MCU & 64KB Flash

| 11.1. | 整體總說明          | 88  |

|-------|----------------|-----|

| 11.2. | 暫存器位址          | 89  |

| 11.3. | 暫存器功能          | 89  |

| 12. 5 | 定時器 TIMER C    | 92  |

| 12.1. | 整體總說明          | 92  |

| 12.2. | 暫存器位址          | 94  |

| 12.3. | 暫存器功能          | 95  |

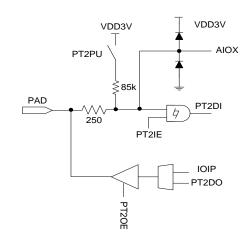

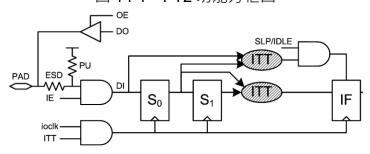

| 13. 🔅 | 通用 GPIO PT2 管理 | 97  |

| 13.1. | 整體總說明          | 97  |

| 13.2. | 暫存器位址          | 100 |

| 13.3. | 暫存器功能          | 100 |

| 13.4. | 類比數位複用功能切換注意事項 | 104 |

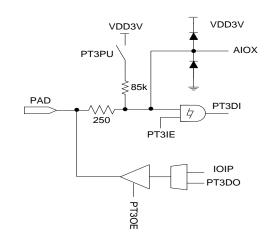

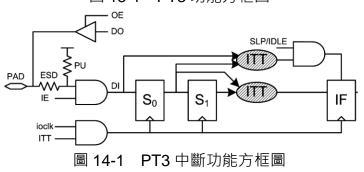

| 14. š | 通用 GPIO PT3 管理 | 105 |

| 14.1. | 整體總說明          | 105 |

| 14.2. | 暫存器位址          | 107 |

| 14.3. | 暫存器功能          | 107 |

| 14.4. | 類比數位複用功能切換注意事項 | 113 |

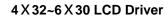

| 15. š | 通用 GPIO PT6 管理 | 114 |

| 15.1. | 整體總說明          | 114 |

| 15.2. | 暫存器位址          | 115 |

| 15.3. | 暫存器功能          | 116 |

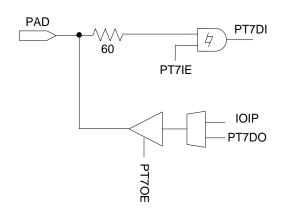

| 16. š | 通用 GPIO PT7 管理 | 122 |

| 16.1. | 整體總說明          | 122 |

## 21-bit ENOB ΣΔADC, 32-bit MCU & 64KB Flash

| 16.2. | 暫存器位址              | 123 |

|-------|--------------------|-----|

| 16.3. | 暫存器功能              | 124 |

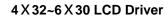

| 17. 通 | i用 GPIO PT8 管理     | 130 |

| 17.1. | 整體總說明              | 130 |

| 17.2. | 暫存器位址              | 131 |

| 17.3. | 暫存器功能              | 131 |

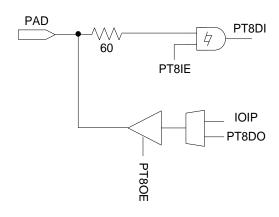

| 18. 通 | 用 GPIO PT9 管理      | 138 |

| 18.1. | 整體總說明              | 138 |

| 18.2. | 暫存器位址              | 139 |

| 18.3. | 暫存器功能              | 139 |

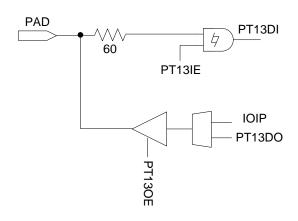

| 19. 通 | i用 GPIO PT13 管理    | 144 |

| 19.1. | 整體總說明              | 144 |

| 19.2. | 暫存器位址              | 145 |

| 19.3. | 暫存器功能              | 145 |

| 20. 通 | i用 GPIO 複用功能管理     | 149 |

| 20.1. | 整體總說明              | 149 |

| 20.2. | 暫存器位址              | 150 |

| 20.3. | 暫存器功能              | 150 |

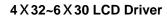

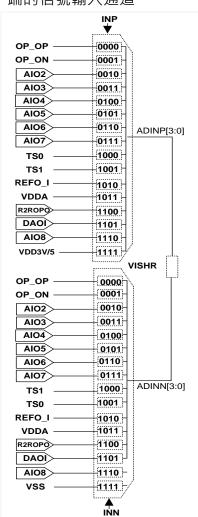

| 21. Σ | ∆ 24 位元類比數位轉換器 ADC | 155 |

| 21.1. | 整體總說明              | 155 |

| 21.2. | 暫存器位置              | 166 |

| 21.3. | 暫存器功能              | 166 |

## 21-bit ENOB ΣΔADC, 32-bit MCU & 64KB Flash

| 22.   | 儀表放大器 IA                    | 170 |

|-------|-----------------------------|-----|

| 22.1. | 整體總說明                       | 170 |

| 22.2. | 暫存器位址                       | 170 |

| 22.3. | . 暫存器功能                     | 171 |

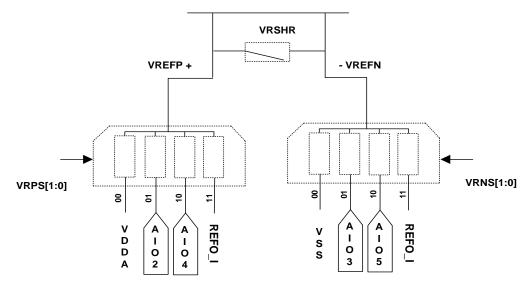

| 23.   | 軌對軌運算放大器 (R2R OPA)          | 173 |

| 23.1. | 整體總說明                       | 173 |

| 23.2. | 暫存器位址                       | 176 |

| 23.3. | . 暫存器功能                     | 176 |

| 24.   | 12-BIT RESISTANCE LADDER 網路 | 180 |

| 24.1. | 整體總說明                       | 180 |

| 24.2. | 暫存器位址                       | 182 |

| 24.3. | . 暫存器功能                     | 182 |

| 25.   | 串列通信 SPI                    | 184 |

| 25.1. | 整體總說明                       | 184 |

| 25.2. | 重存器位址                       | 190 |

| 25.3. | . 暫存器功能                     | 190 |

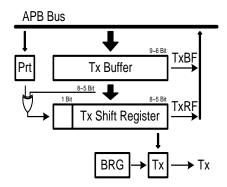

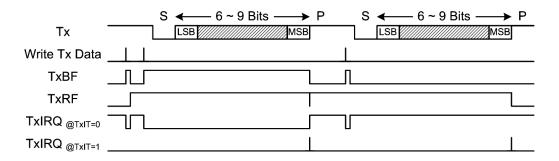

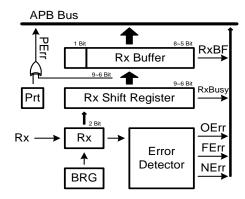

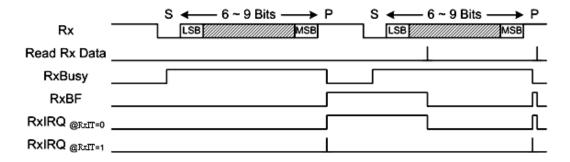

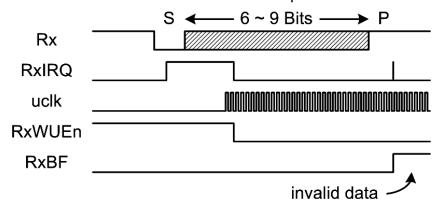

| 26.   | 非同步串列通訊 UART                | 195 |

| 26.1. | 整體總說明                       | 195 |

| 26.2. | 重存器位址                       | 198 |

| 26.3. | . 暫存器功能                     | 198 |

| 26.4. | . UART 使用說明                 | 202 |

| 27.   | 非同步串列通訊 UART2               | 206 |

| 27.1. | . 整體總說明                     | 206 |

## 21-bit ENOB ΣΔADC, 32-bit MCU & 64KB Flash

| 27.2. |                          | 206 |

|-------|--------------------------|-----|

| 27.3. | . 暫存器功能                  | 206 |

| 27.4. | . UART2 使用說明             | 209 |

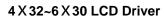

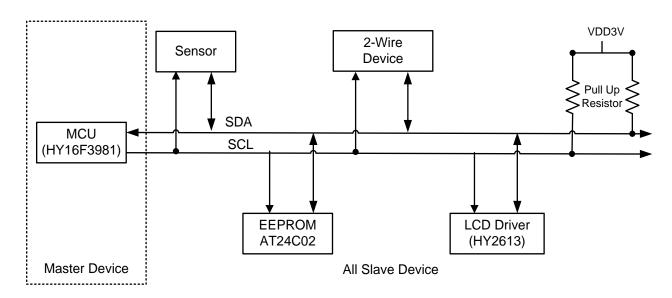

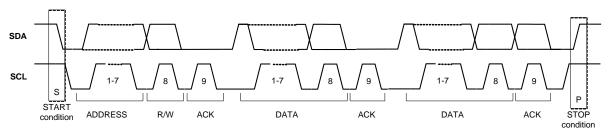

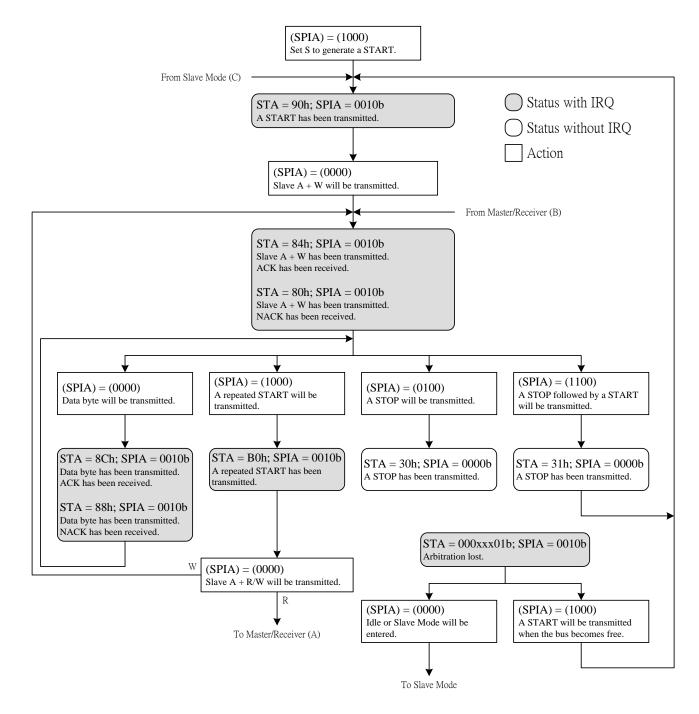

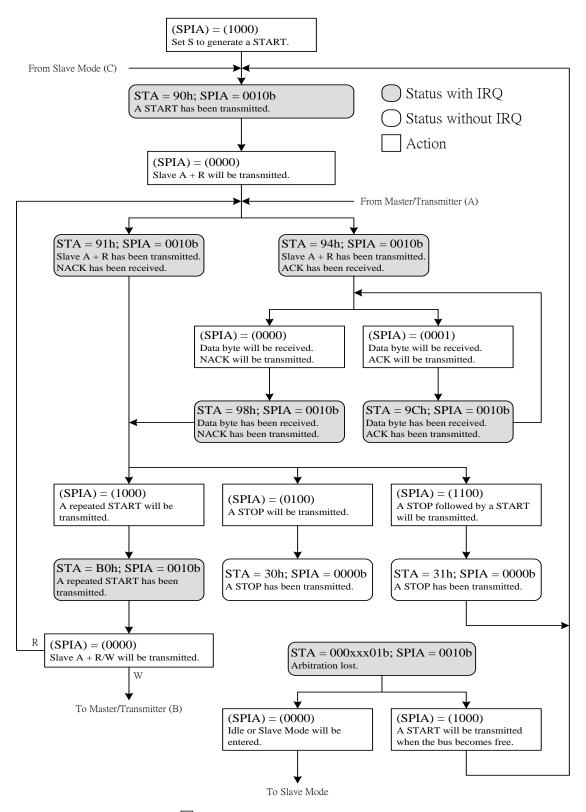

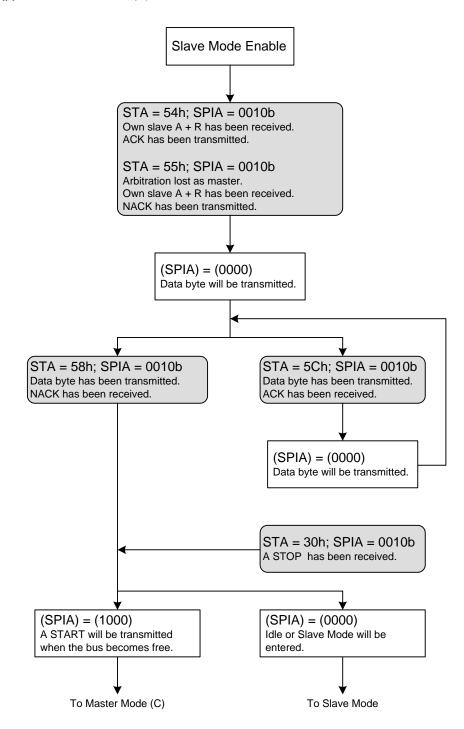

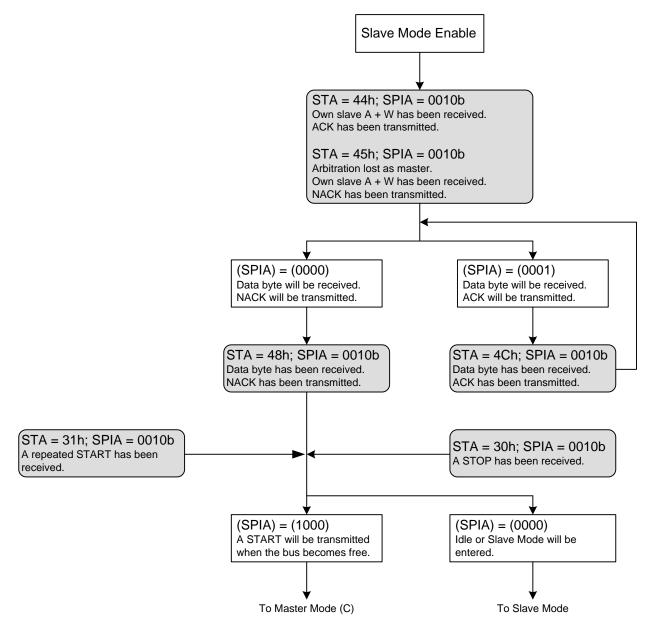

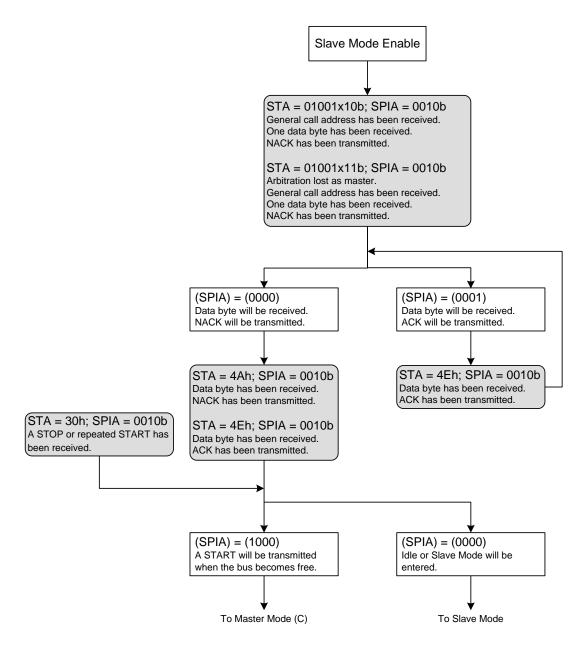

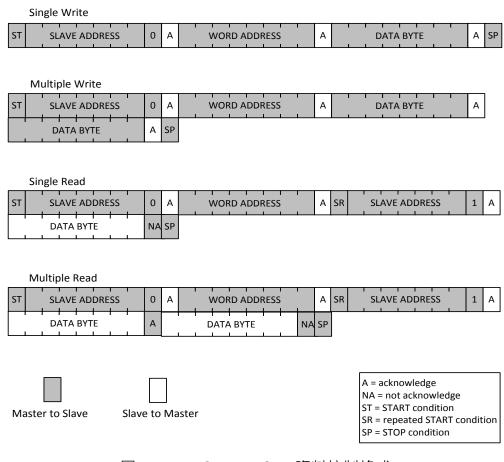

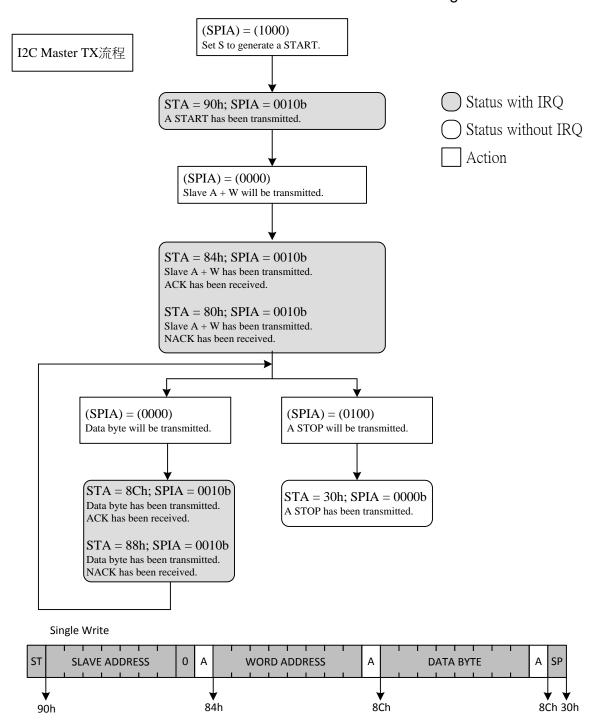

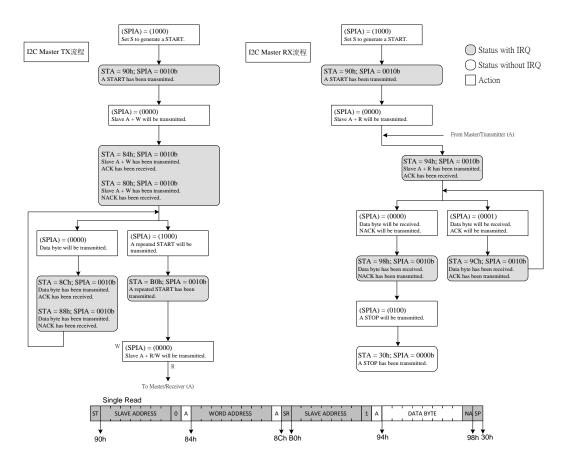

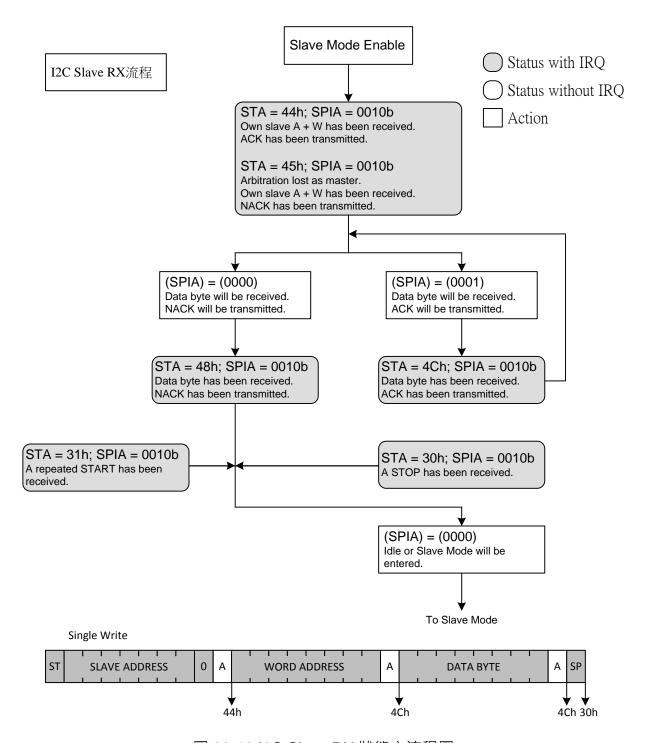

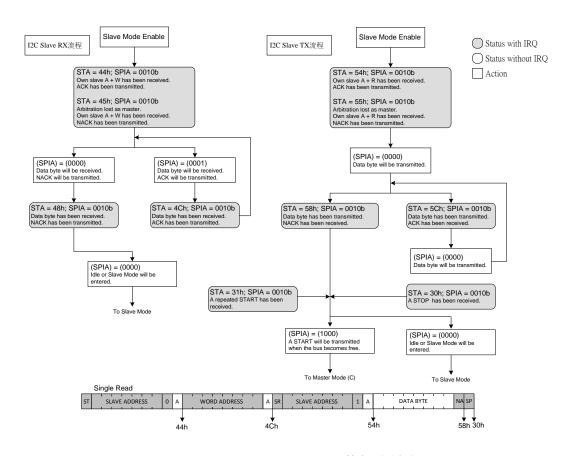

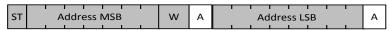

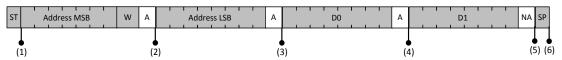

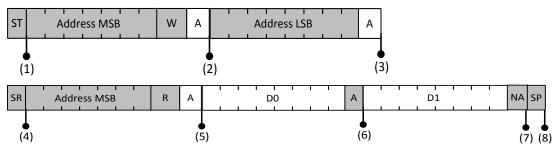

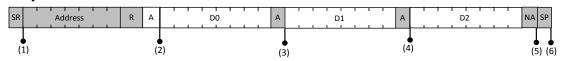

| 28.   | 通用 I2C 通信介面              | 210 |

| 28.1. | 整體總說明                    | 210 |

| 28.2. | . 暫存器位址                  | 220 |

| 28.3. | . 暫存器功能                  | 220 |

| 28.4. | . I2C 使用說明               | 228 |

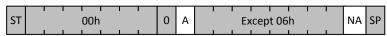

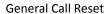

| 28.5. | . I2C General Call Mode  | 238 |

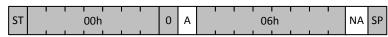

| 28.6. | . 10 Bit Addressing Mode | 239 |

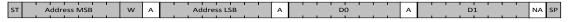

| 28.7. | . 3 Byte Data Mode       | 245 |

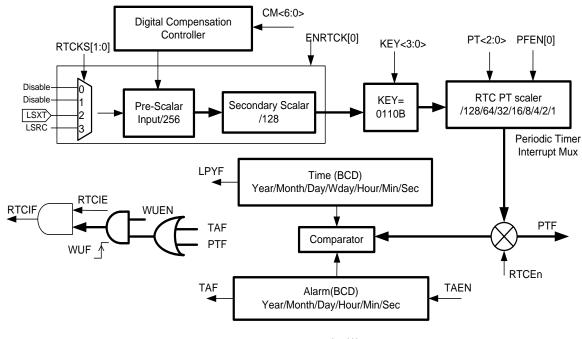

| 29.   | 硬體萬年曆 HW RTC             | 247 |

| 29.1. | . 整體總說明                  | 247 |

| 29.2. | . 暫存器位址                  | 250 |

| 29.3. | . 暫存器功能                  | 250 |

| 30.   | 省電模式介紹                   | 260 |

| 30.1. | . 整體總說明                  | 260 |

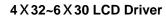

| 31.   | 液晶驅動器 LCD                | 263 |

| 31.1. |                          |     |

| 31.2. | . 暫存器位址                  | 264 |

| 31.3. |                          |     |

| 31.4. |                          |     |

| 31.5. | . LCD 省電功能               | 268 |

21-bit ENOB ΣΔADC, 32-bit MCU & 64KB Flash

#### HY16F3981 User's Guide 21-bit ENOB ΣΔΑDC, 32-bit MCU & 64KB Flash

4X32~6X30 LCD Driver

#### 注意:

- 1、本說明書中的內容,隨著產品的改進,有可能不經過預告而更改。請客戶及時到本公司網站下載更新 http://www.hycontek.com。

- 2、 本規格書中的圖形、應用電路等, 因第三方工業所有權引發的問題, 本公司不承擔其責任。

- 3、本產品在單獨應用的情況下,本公司保證它的性能、典型應用和功能符合說明書中的條件。當使用在客戶的產品或設備中,以上條件我們不作保證,建議客戶做充分的評估和測試。

- 4、請注意輸入電壓、輸出電壓、負載電流的使用條件,使 IC內的功耗不超過封裝的容許功耗。對於客戶在超出說明書中規定額定值使用產品,即使是瞬間的使用,由此所造成的損失,本公司不承擔任何責任。

- 5、本產品雖內置防靜電保護電路,但請不要施加超過保護電路性能的過大靜電。

- 6、本規格書中的產品·未經書面許可·不可使用在要求高可靠性的電路中。例如健康醫療器械、防災器械、 車輛器械、車載器械及航空器械等對人體產生影響的器械或裝置·不得作為其部件使用。

- 7、本公司一直致力於提高產品的品質和可靠度,但所有的半導體產品都有一定的失效概率,這些失效概率可能會導致一些人身事故、火災事故等。當設計產品時,請充分留意冗餘設計並採用安全指標,這樣可以避免事故的發生。

- 8、本規格書中內容,未經本公司許可,嚴禁用於其他目的之轉載或複製。

UG-HY16F3981-V07\_TC

#### 1. 晶片概述

#### 1.1. 簡介

HY16F3981 是一款帶液晶驅動電路(Liquid Crystal Display, LCD)、低功耗、高效能混合信號處理微控制器(Mixed Signal Micro Controller, MCU),適用於做精準的測量和控制,晶片可工作在 2.2V 到 3.6V 的寬電壓範圍,最高可運行到 16MHz,內建 64KByte 的嵌入式快閃記憶體(Flash ROM),以及 8KByte 靜態隨機存取記憶體(SRAM)。HY16F3981 集成了高精度 24-bit 調變類比轉換器( $\Sigma\Delta ADC$ ),軌對軌運算放大器(OPAMP),12-Bit Resistance Ladder,硬體實現的即時時鐘 Hardware RTC),提供高性能外圍接口,如 UART、SPI、I2C、GPIO,及內建的電源管理系統等功能。支援低電壓檢測,多個外圍接口喚醒功能。且支援 C/C++開發平台的 32-bit 微控制器。豐富的資源可以讓設計者完成一個低電源低成本的混合信號處理系統。

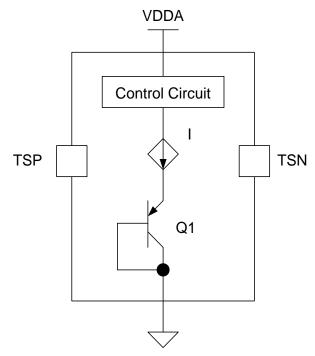

這款控制器中的類比前端電路包含了一個 12-bit resistance ladder、一個軌對軌運算放大器(OPA)。其中 12 位元的數位類比轉換器保證單調性,是一個梯形數位電阻器,每一個最低有效位元(LSB)接近 200 歐姆,該電阻具有低溫係數。軌對軌運算放大器有一個輸入網路,可應用於差分類比電路配置,例如積分器、電流電壓轉換器、可編程增益放大器、和連續漸進式類比數位轉換器。

超低噪音 24-bit 類比數位轉換器(ADC)是嵌入式的。最大輸出率為 15KSPS 且具 21-bit 有效位元數(ENOB, Effective Number Of Bit),最小可解析輸入訊號為 1.1uV RMS Noise (Root- Mean- Square),ADC 前端內建儀表放大器 IA,最大輸入放大倍率高達 256 倍放大倍率。

電源管理提供可選擇的類比電路調節電壓,可做為電壓基準源,與傳感器電源驅動。CPU 核工作電源也是由內部的線性穩壓電源所提供。64KByte 嵌入式快閃記憶體,可用來執行程 式及儲存資料。資料也可以在程式執行期間被儲存在快閃記憶體中。同時內建 8KByte 靜態 隨機存取記憶體供系統使用。

採用 32-bit 高效能混合信號處理微控制器核心,可以使每一時脈週期(Clock Cycle)執行一個指令,最高可達 16MIPS(Millions of Instructions Per Second),具低耗電量指標。紘康科技提供了一些容易使用的程式撰寫工具,使用者可在開發平台下撰寫 C/C++語言或組合語言的程式。晶片帶有電路仿真功能,提供容易除錯的環境。晶片可在 2.2V 到 3.6V 的工作電壓,-40°C 到 85°C的溫度環境下工作。

UG-HY16F3981-V07\_TC

## 1.2. 型態說明表

## 暫存器位元型態說明表

| 設定型態     | 描述                                                | 初始值                    |

|----------|---------------------------------------------------|------------------------|

| -        | No Use                                            |                        |

| RSV.     | Reserve                                           |                        |

| X        | Unknown                                           |                        |

| W        | Write                                             |                        |

| R        | Read                                              |                        |

| R0       | Only Read 0                                       |                        |

| R1       | Only Read 1                                       |                        |

| W0       | Only Write 0                                      |                        |

| W1       | Only Write 0                                      |                        |

| RW-0     | Read/ Write                                       | Initial 0              |

| RW-1     | Read/ Write                                       | Initial 1              |

| R0W-0    | Read 0/ Write                                     | Initial 0              |

| R1W-1    | Read 1/ Write                                     | Initial 1              |

| R-X      | Read                                              | Initial 1 or 0 Unknown |

| []       | Register length (暫存器長度)                           |                        |

| <>       | Register value (暫存器內容)                            |                        |

| ABC[7:0] | ABC register had 0 to 7bit (ABC 暫存器總共有 8          |                        |

|          | 位元)                                               |                        |

| ABC<111> | ABC register had 3bit and value had 111 of binary |                        |

|          | (ABC暫存器總共有3位元·內容為二進制111)                          |                        |

| ABC<11x> | x : can be neglected, it can be set as 1 or 0     |                        |

|          | (ABC暫存器總共有3位元·內容為二進制。可為110                        |                        |

|          | 或111                                              |                        |

UG-HY16F3981-V07\_TC

## 2. 功能概述

## 2.1. 方塊圖

圖 2-1 晶片功能架構圖

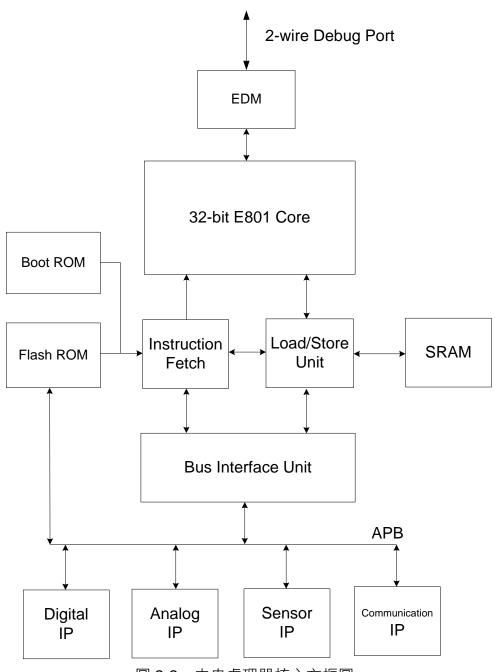

#### 2.2. 中央處理器核心方框圖

圖 2-2 中央處理器核心方框圖

UG-HY16F3981-V07\_TC

page13

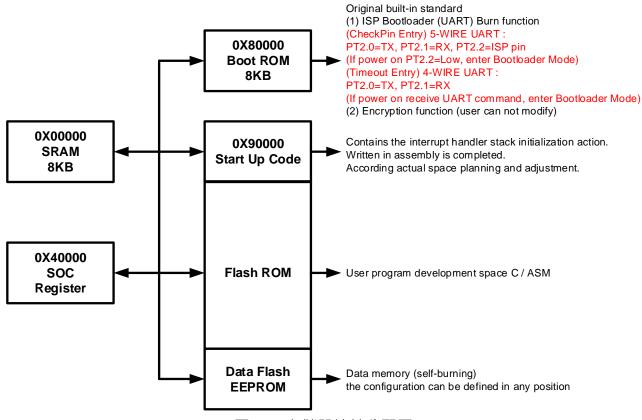

#### 3. 記憶體結構

#### 3.1. 記憶體說明

HY16F3981 系列產品所使用的中央處理器(CPU)

內核是 Andes 32-bit CPU。微控制器的存儲器地址分配如下:

0x00000 to 0x01FFF 靜態隨機存取記憶體, SRAM (8K Byte)

0x40000 to 0x4FFFF 系統控制暫存器,SOC Register

0x80000 to 0x81FFF 開機區塊記憶體,Boot ROM (8K Byte): 可支持(Timeout Entry)4線式與 (CheckPin Entry) 5線式 UART 傳輸 ROM ISP Bootloader 功能. 晶片預設不開啟此功能,需透過燒錄器進行燒錄設定或代燒程式才能開啟此功能.

0x90000 to 0x9FFFF 主程式區塊快閃記憶體,Main Program Flash ROM (64K Byte)

圖 3-1 存儲器地址分配圖

© 2016-2021 HYCON Technology Corp www.hycontek.com

#### 3.2. 記憶體位址

微控制器詳細的系統控制暫存器(SOC Register)位址分配如下表。

| 功能模塊                           | 描述                                                | Base Address |

|--------------------------------|---------------------------------------------------|--------------|

| INT                            | 中斷向量控制暫存器(Interrupt Control)                      | 0x40000      |

| SoC                            | 系統控制暫存器(System)                                   | 0x40100      |

| CLK                            | 頻率系統控制暫存器(Clock System)                           | 0x40300      |

| PMU                            | 電源系統控制暫存器(Power Management)                       | 0x40400      |

| MC                             | 記憶體控制暫存器(Memory Controller)                       | 0x40600      |

| PIO                            | 通用型之輸入輸出埠控制暫存器(GPIO Port Control)                 | 0x40800      |

| TMR                            | 計數器控制暫存器(Timer Register)                          | 0x40C00      |

| UART                           | UART 通訊界面控制暫存器(UART Mode)                         | 0x40E00      |

| SPI                            | SPI 通訊界面控制暫存器(SPI Mode)                           | 0x40F00      |

| I <sup>2</sup> C               | I <sup>2</sup> C 通訊界面控制暫存器(I <sup>2</sup> C Mode) | 0x41000      |

| ADC                            | 類比數位轉換器控制暫存器(Analog-to-Digital Module)            | 0x41100      |

| IA                             | 儀表放大器控制暫存器(IA)                                    | 0x41600      |

| 12-bit<br>resistance<br>ladder | 數位電阻器控制暫存器(Resistance Ladder Module)              | 0x41700      |

| R2R OPAMP                      | 軌對軌運算放大器控制暫存器(Operational Amplifier)              | 0x41900      |

| RTC                            | 硬體萬年曆 RTC 暫存器(Real Time Clock)                    | 0x41A00      |

| LCD                            | 液晶顯示驅動控制暫存器(LCD)                                  | 0x41B00      |

表 3-1 系統控制暫存器

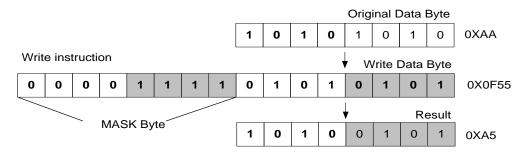

部分重要暫存器都含有遮蔽位元(MASK Bit),如下圖 3-3 說明。MASK 是用於使能對應控制位元的寫入,只有在與控制位元對應的 MASK 位元為<1>時,對應的控制位元才能寫入值,否則寫入動作會無效,無法真正修改暫存器的值。如圖 3-2 所示。

暫存器長度總共有 32 位元,大部分有 16 位元 MASK Bit。MASK Bit 分為兩組 8 位元,每 8 位元 MASK 控制著相應 8 位元控制暫存器位元。根據寄存器的內容分佈:BIT[31:24]控制著 BIT[23:16],而 BIT[15:8]控制著 BIT[7:0]。只有在 MASK Bit 置<1>的情況下,對應的控制位元才能寫入有效值。

如:要對 BIT[5:0]寫入 101010b‧則寄存器操作方式寫入值為:0011111100101010b。 其中 00111111b 是 BIT[15:8]的 MASK BIT‧可使能 BIT[5:0]對應控制位元寫入值有效‧而 00101010b 就是對 BIT[5:0]寫入的值。

INT Base Address + 0X10 (0X40010)

| Symbol |         | INTPT1 (PT1 Interrupt Control Register) |        |        |        |        |        |        |        |

|--------|---------|-----------------------------------------|--------|--------|--------|--------|--------|--------|--------|

| Bit    | [31:24] | [23]                                    | [22]   | [21]   | [20]   | [19]   | [18]   | [17]   | [16]   |

| 名稱     | MASK    | PT17IE                                  | PT16IE | PT15IE | PT14IE | PT13IE | PT12IE | PT11IE | PT10IE |

| RW     | R0W-0   |                                         | RW-0   |        |        |        |        |        |        |

| Bit    | [15:08] | [7]                                     | [6]    | [5]    | [4]    | [3]    | [2]    | [1]    | [0]    |

| 名稱     | MASK    | PT17IF                                  | PT16IF | PT15IF | PT14IF | PT13IF | PT12IF | PT11IF | PT10IF |

| RW     | R0W-0   | RW0-0                                   |        |        |        |        |        |        |        |

圖 3-2 暫存器的基本結構

### 3.3. 靜態隨機存取記憶體(SRAM)

HY16F3981 帶有 8KByte 靜態隨機存取記憶體。起始位址是從 0x0000 到 0x1FFF。MCU可選擇一個位元組(One Byte)、兩個位元組(Half Word)、或四個位元組(One Word)的存取。可以在一個 Clock Cycle 存取四個位元組(One Word)資料。

### 3.4. 快閃記憶體(Flash ROM)

HY16F3981 帶有 64KByte 的嵌入式快閃記憶體。起始位置是從 0x90000 到 0x9FFFF。使用者可將程式碼儲存在快閃記憶體。要編寫快閃記憶體的程式碼,使用者需用 CPU 指令來讀寫快閃控制單元。使用者可以選擇區塊間的任何位置儲存資料。

UG-HY16F3981-V07\_TC

#### 3.5. 匯流排介面單元

匯流排的結構中,暫存器的讀寫是由一個 32 位元的高階週邊匯流排(Advanced Peripheral Bus, APB)所控制。可在一個 Clock Cycle 寫入一個 32 位元的資料。而為了防止資料寫入期間去覆蓋掉已寫入的資料值,則可使用了 MASK 遮罩的功能來完成。

如圖 3-3 說明,原始寄存器中 BIT[7:0]資料為 10101010b,透過 MASK BIT 的控制使寫入資料有效,當操作 BIT[15:0],寫入資料 00001111010101b,則結果為:

000000010100101b。表示 MASK Bit 只可設置 1b、回讀時皆為 0b、而 BIT[7:4]雖然要寫 入 0101b、但是 BIT[15:12]定義為 0000b、因此代表 BIT[7:4]的寫入值是無效;而 BIT[3:0] 要寫入 0101b、且同時 MASK BIT[11:8]定義為 1111b、因此代表 BIT[3:0]的寫入值可以有效。

圖 3-3 數據 MASK 結構

UG-HY16F3981-V07\_TC

#### 3.6. 開機記憶體(Boot ROM)

8KByte 的開機記憶體。起始位址是從 0x80000 到 0x81FFF。該區塊空間是給開機碼、(Flash)快閃控制碼、和安全保護碼所使用。當晶片重置時,程式計數器會從 0x80000 開始。開機記憶體中的軟體涵蓋許多訊息,包含系統程式協定、和安全協定等。

#### 3.7. 嵌入式除錯模組(EDM)

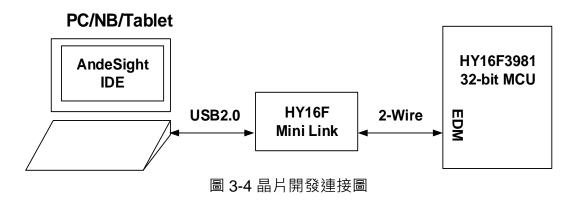

嵌入式除錯模組(Embedded Debug Module, EDM)為晶片在開發環境下可使用的除錯介面。在晶片未設定安全性保護下,使用者可以透過 EDM 介面傳送指令給 MCU,進而讀取除錯模式中的訊息。EDM 是晶片和電腦溝通的橋樑,透過 HY16F Mini Link 連結 PC USB 以及晶片 EDM,僅使用兩線協定介面。EDM 可以透過 APB 存取晶片的控制暫存器、一般用途的GPR 暫存器、SRAM DLM、以及 Flash ROM ILM。

UG-HY16F3981-V07\_TC

## 4. 系統暫存器

#### 4.1. 整體總說明

管理系統的工作模式及晶片的復位狀態,如看門狗、外部復位、欠電壓復位等。

#### 4.2. 暫存器位址

| SOC Status Register Address             | 31 | 24 | 23 | 16 | 15  | 8   | 7  | 0  |

|-----------------------------------------|----|----|----|----|-----|-----|----|----|

| SOC Status Base Address + 0X04(0X40104) | .  | -  |    | -  | MAS | SK0 | RE | G0 |

-保留

#### 4.3. 暫存器功能

操作該寄存器 0x40104[4]可以對系統工作模式設置為休眠模式(SLEEP)/待機模式 (IDLE)。查詢該寄存器 0x40104[3]可知晶片處於什麼樣的工作狀態下。

© 2016-2021 HYCON Technology Corp

UG-HY16F3981-V07\_TC

## 系統暫存器 SOC

|        | SOC Status Base Address + 0X04 (0X40104) |                     |                  |                   |      |                       |         |                  |                  |

|--------|------------------------------------------|---------------------|------------------|-------------------|------|-----------------------|---------|------------------|------------------|

| Symbol |                                          | SOC Status Register |                  |                   |      |                       |         |                  |                  |

| Bit    |                                          |                     | [31:24]          |                   |      |                       | [23     | :16]             |                  |

| 名稱     | ICE Configuration SO                     |                     |                  |                   |      |                       | SOC Con | figuration       |                  |

| RW     |                                          |                     | R-0X0F           |                   |      | R-0X1C                |         |                  |                  |

| Bit    | [15:8]                                   | [7]                 | [6]              | [5]               | [4]  | [3]                   | [2]     | [1]              | [0]              |

| 名稱     | MASK                                     | -                   | F <sub>PRG</sub> | F <sub>CRst</sub> | IDLE | F <sub>SLP/IDLE</sub> | FwDog   | F <sub>RST</sub> | F <sub>BOR</sub> |

| RW     | R0W-0 - RW0-0                            |                     |                  |                   |      |                       |         | RW0-1            |                  |

| 位元                       | 名稱                    | 描述                                     |

|--------------------------|-----------------------|----------------------------------------|

|                          |                       | Power Good 旗標                          |

| Bit[06] F <sub>PRG</sub> |                       | _ 0 正常                                 |

|                          |                       | 1 Power Good 曾經被觸發                     |

|                          |                       | CPU Core 復位旗標                          |

| Bit[05]                  | F <sub>CRST</sub>     | 0 正常                                   |

|                          |                       | 1 ICP Core 曾經被觸發                       |

|                          |                       | 待機模式控制位元                               |

| Bit[04]                  | IDLE                  | 0 休眠模式(Sleep Mode)                     |

|                          |                       | 1 待機模式 (IDLE Mode )                    |

|                          |                       | 休眠(Sleep)/待機(Idle Flag)                |

| Bit[03]                  | F <sub>SLP/IDLE</sub> | (低電壓復位或復位電路復位可清零該位元)                   |

| Dit[03]                  |                       | 0 正常                                   |

|                          |                       | 1 晶片進入休眠模式(Sleep Mode)或待機模式(Idle Mode) |

|                          |                       | 看門狗(WDT)旗標(低電壓復位或外部復位可清零該位元)           |

| Bit[02]                  | Fwdt                  | 0 正常                                   |

|                          |                       | 1 看門狗產生復位或者中斷                          |

|                          |                       | 外部復位旗標(低電壓復位(BOR)可清零該位元)               |

| Bit[01]                  | F <sub>RST</sub>      | 0 正常                                   |

|                          |                       | 1 Reset PIN 復位或者 ICP 軟件復位已發生           |

|                          |                       | 低電壓復位(BOR)旗標(晶片電壓高於 1.8V 自動清理)         |

| Bit[00]                  | F <sub>BOR</sub>      | 0 正常                                   |

|                          |                       | 1 低電壓復位已發生                             |

UG-HY16F3981-V07\_TC

#### 5. 電源管理

#### 5.1. 整體總說明

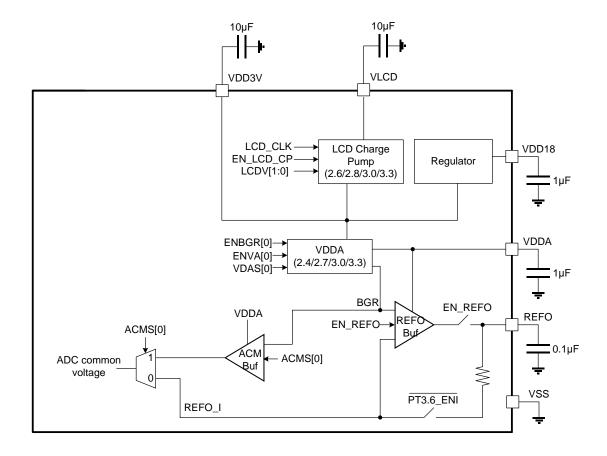

電源管理模塊包括一個粗 Band Gap 基準、一個細 Band Gap 基準、一個 VDDA LDO、一個 VDD18 LDO、以及基準輸出緩衝器。晶片 VDD3V 只需要一個電壓源來運轉,這運轉電壓源介於 2.2V 到 3.6V 之間。電源系統可分成三個部份: 輸入/輸出電路、類比電路、和數位電路。輸入/輸出電路的電源是由 VDD3V 所驅動。類比電路電源是由內部的 VDDA LDO 所驅動。最後,數位電路的電源是由 VDD18 LDO 所驅動。當 MCU 在待機模式,晶片以最低的功耗來維持暫存器和 SRAM 的資料存儲操作。在待機模式中,粗 Band Gap 基準、BOR、和 VDD18 LDO 是開啟的。若在自動喚醒模式,低速振盪器需要被開啟。

UG-HY16F3981-V07\_TC

#### (01)晶片工作電壓 VDD3V 及 VDD18:

晶片工作電壓是通過管腳 VDD3V 輸入,電壓範圍是 2.2V~3.6V,且在管腳端需要接入 一個 10uF 的對地電容,可使這 VDD3V 電壓更穩定。VDD18 LDO 通過管腳 VDD18 輸出穩 壓電壓 1.8V,目管腳端需要接入一個 1uF 的旁路電容器。

#### (02)VDDA 電壓:

晶片帶有一個轉為類比電路使用的穩壓電路 LDO: VDDA·使用 ADC 時必須開啟 VDDA電壓。它可設置不同的操作模式和不同的輸出電壓。它有四個不同的操作模式,第一個模式是與 VDD3V 短路,此時 VDDA 接近 VDD3V;第二個模式是接地放電(Weak Pull Down),此時 VDDA輸出接近 VSS 電位;第三個模式是高阻態(High Z)·可從外部灌入電壓給 VDDA,但是外部灌入的電壓應該不可超過 VDD3V;第四個模式是可調節穩壓模式 LDO,此模式 VDDA輸出四個不同的電壓:2.4V、2.7V、3.0V、和3.3V。要有更好的效能,VDD3V-VDDA壓差應該要大於0.2V,且可驅動達到10mA。它也需要在管腳 VDDA接入一個1uF的旁路電容器。注意,當 VDDA接入一個1uF對地電容時,VDDA的穩定時間至少需要大於0.5ms,當 VDDA接入一個10uF對地電容時,VDDA的穩定時間至少需要大於1ms。

### (03)低電壓檢測電路(BOR):

BOR 電路是用來監控電源系統和 MCU 的穩定度。當 VDD3V 或 VDD18 的電壓低於 BOR 值測電壓就會被觸發,系統因而被重設,晶片產生復位,直到晶片工作電壓達到 BOR 電壓 1.8V 以上才會恢復正常工作。

UG-HY16F3981-V07\_TC

### (04)參考電壓和共模電壓(REFO):

當 VDDA 高於 2.4V·類比電路就可運轉。但是,類比電路要求提供電流偏差和參考電壓。因此,在啟動類比電路之前啟動 Band Gap 參考電壓,將暫存器 PMU[4](ENBGR)設定為 1便可啟動 Band Gap 參考電壓。只有開啟 Band Gap 參考電壓後,共模電壓(REFO)才有效輸出 1.2V。要啟動 ADC,需要為 ADC 提供一個共模電壓(REFO)。這個共模電壓可選擇外部或內部的電源。若要選擇內部電源,就要將 ACMS 設定為 1。若要選擇外部電源,就要將 ACMS 設定為 0,同時需要輸出一個共模電壓(REFO)。使用者因應用會需要一個基準電壓來驅動外部電路。就可以將 ENRFO 設定為 1,將共模電壓輸出至管腳,且 REFO 是具有緩衝器的 Band Gap 基準電壓。REFO 管腳輸出電壓大約是 1.2V 且具有+/-1mA 的推拉驅動能力。它可以驅動一個 22~1000nF 的大型電容器承載。如果使用了外部的 REFO 電壓輸出,此時 ADC 使用的共模電壓則可用外部電源,將 ACMS 設定為 0,可節省電力。注意,當 REFO 接入一個 0.1uF 對地電容時, REFO 的穩定時間至少需要大於 0.1ms。

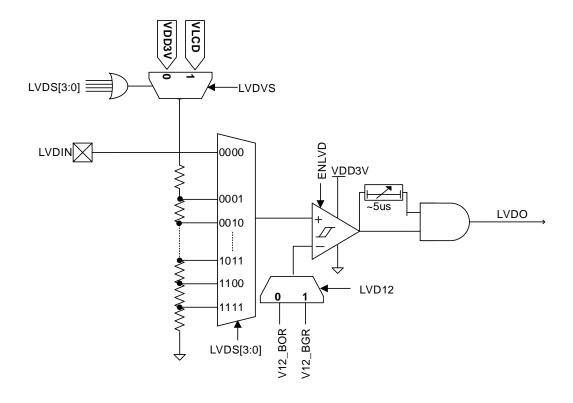

#### (05) LVD 低電壓檢測:

LVD 低電壓檢測針對工作電壓 VDD3V 與 VLCD 電壓或外部輸入電壓 LVDIN,提供可設置的低電壓偵測功能,當輸入電壓達到低電壓偵測點時,則暫存器 LVDO 置 0。同理,當輸入電壓高於低電壓偵測點時,則暫存器 LVDO 置 1;LVD 參考電壓源為可選擇 BOR 或 BGR(即Band Gap 參考電壓)。當輸入電壓為外部電壓 LVDIN 時,低電壓偵測點設置 LVDS 需設置為0000b,此時低電壓偵測點為 1.2V,即 BOR 或 BGR 實際電壓大小;當輸入電壓為 VDD3V或 VLCD 時,低電壓偵測點 LVDS 設置範圍為 0001b~1111b(2.0V~3.4V)。

#### 設置流程:

- (1) 選擇輸入電壓,若為外部輸入電壓 LVDIN 則不需對暫存器 LVDS 設置,或透過 LVDVS 設置選擇 VDD3V 或 VLCD

- (2) 選擇參考電壓·透過 LVD12 設置選擇 V12\_BOR 或 V12\_BGR. 當選擇 V12\_BGR 時,需要先開啟 Band Gap 電壓源才能使用(即 0x40400[4]=1b),選擇 V12\_BOR 不需做任何額外電壓源開啟動作

- (3) 設置低電壓偵測點,若為外部輸入電壓 LVDIN 則 LVDS 設置為 0000b,若為 VDD3V 或 VLCD 則 LVDS 設置低電壓偵測點 0001b~1111b(2.0V~3.4V)

- (4) 致能低電壓比較器 ENLVD,開始低電壓偵測

UG-HY16F3981-V07\_TC

下表展示各部份模塊使用的電壓源。

| Block 名稱            | 電壓源          | Block 名稱                 | 電壓源   |

|---------------------|--------------|--------------------------|-------|

| 32-bit CPU Core     | VDD18        | Timer A/B/C PWM          | VDD18 |

| 08KB SRAM           | VDD18        | GPIO Port                | VDD3V |

| 64KB Flash ROM      | VDD3V/ VDD18 | 24-bit SD ADC            | VDDA  |

| Clock System        | VDD18        | 12-bit Resistance ladder | VDDA  |

| Watch Dog Timer     | VDD18        | Rail-to-Rail OPAMP       | VDDA  |

| Hardware RTC        | VDD18        |                          |       |

| BOR                 | VDD3V/ VDD18 |                          |       |

| Band Gap/Reference  | VDDA         |                          |       |

| Hardware EUART      | VDD18/VDD3V  |                          |       |

| 32-bit Hardware SPI | VDD18/VDD3V  |                          |       |

| Hardware I2C        | VDD18/VDD3V  |                          |       |

表 5-1 晶片電源分佈

UG-HY16F3981-V07\_TC

#### 5.2. 暫存器位址

| Power Management Register Address | 31 2 | 24  | 23 | 16   | 15  | 8   | 7  | 0  |

|-----------------------------------|------|-----|----|------|-----|-----|----|----|

| PMU Base Address + 0x00 (0x40400) | MASK | (1  | RE | EG1  | MAS | SK0 | RE | G0 |

| PMU Base Address + 0x08 (0x40408) | R    | ₹sv |    | REG3 | MAS | SK0 | RE | G2 |

## 5.3. 暫存器功能

## 電源管理暫存器 PMU

|        | Power Management Base Address + 0x00 (0x40400) |                                   |     |      |     |     |     |  |  |

|--------|------------------------------------------------|-----------------------------------|-----|------|-----|-----|-----|--|--|

| Symbol | PMU0 (PMU Control Register 0 )                 |                                   |     |      |     |     |     |  |  |

| Bit    | [31:24]                                        | [31:24] [23:20] [19:18] [17:16]   |     |      |     |     |     |  |  |

| 名稱     | MASK                                           | MASK - VDAS ENVA                  |     |      |     |     |     |  |  |

| RW     | R0W-0                                          |                                   |     | RW-0 |     |     |     |  |  |

| Bit    | [15:08]                                        | [7:5]                             | [4] | [3]  | [2] | [1] | [0] |  |  |

| 名稱     | MASK                                           | MASK - ENBGR ACMS Rsv ENRFO VDDLP |     |      |     |     |     |  |  |

| RW     | R0W-0                                          | R0W-0 RW-0                        |     |      |     |     |     |  |  |

| 位元          | 名稱    | 描述       |                                                    |

|-------------|-------|----------|----------------------------------------------------|

| Di4[40, 40] | VDAS  | 00       | A 輸出電壓選擇 VDDA =2.4V                                |

| Bit[19~18]  | VDAS  | 10<br>11 | VDDA =2.7V<br>VDDA =3.0V<br>VDDA =3.3V@VDD3V>=3.5V |

|             |       | VDDA     | A LDO 電壓源設置·控制 VDDA 輸出電壓值範圍                        |

|             |       | 00       | 高阻抗(High Z)                                        |

| Bit[17~16]  | ENVA  | 01       | 內部短接至 VDD3V·VDDA 輸出值接近 VDD3V                       |

|             |       | 10       | 下拉(Weak pull down),VDDA 只輸出接近 VSS 電位               |

|             |       | 11       | VDDA LDO、VDDA 可調輸出、由 VDAS 決定                       |

|             |       | Band     | Gap 電壓開啟控制                                         |

| Bit[04]     | ENBGR | 0        | 關閉                                                 |

|             |       | 1        | 開啟                                                 |

|             |       | ADC      | 類比地輸入源選擇                                           |

| Bit[03]     | ACMS  | 0        | 外部類比地                                              |

|             |       | 1        | 內部類比地·(搭配 ADC 使用)                                  |

|             |       | 共模電      | 图壓(REFO)開啟控制                                       |

| Bit[01]     | ENRFO | 0        | 關閉                                                 |

|             |       | 1        | 開啟                                                 |

|             |       | VDD1     | 8 LDO 低功耗控制                                        |

| Bit[00]     | VDDLP | 0        | 正常(從休眠喚醒後該位元需被置 0)                                 |

|             |       | 1        | 低功耗                                                |

UG-HY16F3981-V07\_TC

## 電源管理暫存器 PMU1

|        | Power Management Base Address + 0x08 (0x40408) |                               |     |     |      |      |  |  |  |

|--------|------------------------------------------------|-------------------------------|-----|-----|------|------|--|--|--|

| Symbol |                                                | PMU1 (PMU Control Register 1) |     |     |      |      |  |  |  |

| Bit    |                                                | [31:17]                       |     |     |      | [16] |  |  |  |

| 名稱     |                                                | Rsv                           |     |     |      |      |  |  |  |

| RW     |                                                | R-0                           |     |     |      | R-X  |  |  |  |

| Bit    | [15:08]                                        | [7:4]                         | [3] | [2] | [1]  | [0]  |  |  |  |

| 名稱     | MASK LVDS Rsv LVD12 LVDVS                      |                               |     |     |      |      |  |  |  |

| RW     | R0W-0                                          | RW-0                          | R-0 |     | RW-0 | •    |  |  |  |

| 位元       | 名稱    | 描述                                                                                                                                                                                                               |

|----------|-------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Bit[16]  | LVDO  | LVD Output         0       當負端電壓 > 正端電壓時, LVDO=0         1       當正端電壓 > 負端電壓時, LVDO=1                                                                                                                           |

| Bit[7~4] | LVDS  | LVDS 正端電壓值  0000 1.2V,外部輸入電壓 LVDIN. (從晶片外部輸入電壓到 PT3.4)  0001 2.0V  0010 2.1V  0011 2.2V  0100 2.3V  0101 2.4V  0110 2.5V  0111 2.6V  1000 2.7V  1001 2.8V  1010 2.9V  1011 3.0V  1110 3.1V  1110 3.3V  1111 3.4V |

| Bit[02]  | LVD12 | LVD 負端電壓源  0 V12_BOR  1 V12_BGR(form bandgap output, precised)                                                                                                                                                   |

| Bit[01]  | LVDVS | LVD 正端電壓源  0 VDD3V  1 VLCD                                                                                                                                                                                       |

| Bit[00]  | ENLVD | LVD Enable  0 Disable 1 Enable                                                                                                                                                                                   |

UG-HY16F3981-V07\_TC

#### 6. 時脈系統

#### 6.1. 整體總說明

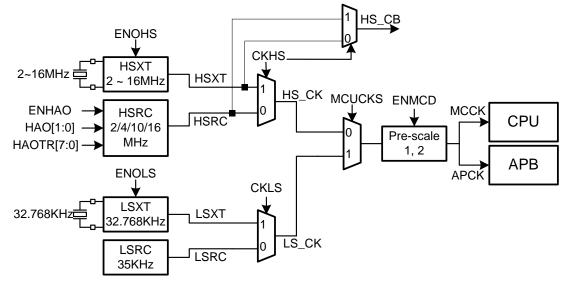

時脈控制系統為整個晶片提供時脈,包括系統時脈(CPU時脈、APB時脈)及所有外圍外設工作時脈(定時器、通訊介面、RTC、類比電路等外圍設備)。各個功能模塊的時脈都帶有時鐘開關控制器,時脈源選擇及除頻器。在休眠模式下,控制器始終關閉外部晶振、內部晶振及系統時脈使系統功耗降到最低。工作時脈源具有外部晶振、內部 HAO 與 LPO 震盪器,透過除頻器可彈性分配與管理 CPU 及外圍設備的頻率源調整晶片功耗,達到節約功耗目的。

#### 6.1.1. 外部震盪器

外部震盪器有兩組、分別為高速晶振(HSXT)和低速晶振(LSXT)。晶片帶有高速和低速外部晶振兩組獨立輸入管腳、所以用戶可以同時接上兩組外部晶振。外部晶振需要並聯一個電阻,否則即使焊接了晶振、也無法正常起震、同時必須要焊接兩個 0~20pF 的對地電容、對地電容值大小需要視電路板佈局產生的技生電容效應評估。其震盪器引腳間的並聯電阻(R1)、與震盪器各別引腳電容 C2/C1 參數隨外接不同頻率、不同品牌的晶振及電路板佈局方式而有所差異。下表列出 R1/C1/C2 參數與頻率源配置建議值,供使用參考。

|      |      |         | 外部晶排 |      |      | 指令執           | 行狀態          |

|------|------|---------|------|------|------|---------------|--------------|

| 型式   | 符號   | 頻率      | R1/Ω | C1   | C2   | Sleep<br>Mode | Idle<br>Mode |

| 低速震盪 | LSXT | 32768Hz | 10M  | 10pF | 10pF | 停止            | 可設置          |

| 高速震盪 | HSXT | 2~16MHz | 1M   | 10pF | 10pF | 停止            | 可設置          |

表 6-1 外部晶振配置建議

注意: 外部震盪器引腳電容 C1/C2 大小,可依照實際 PCB 電路板布局與不同的晶震視情況 選擇調整其電容值大小,建議範圍為 0~20pF。

#### 使用外部晶震注意事項:

- (01)使用 16MHz 時,晶片工作電壓必須大於 3.0V。

- (02)外接晶震 4MHz/8MHz 的穩定時間約為 30ms。

- (03)外接 32768Hz 晶震的穩定時間約為 1.3s。

- (04)執行休眠 Sleep 指令後,外部晶震皆會停止震盪。

- (05)外接晶震時,需要注意引腳的輸入/輸出配置,使用時需將引腳設置不得配置內部上拉電阻,以免操作時發生異常。且外部電阻 R1 絕對不能缺省。

UG-HY16F3981-V07\_TC

(06)要使用外部震盪器(HSXT),則建議選擇 MCU clock/2 的設計,可降低震盪器頻率源受到干擾,強化抗干擾能力。

#### 6.1.2. 內部晶振 HAO 與 LPO

HAO 為晶片內部高速 RC 震盪器輸出典型頻率值為 2MHz/4MHz/10MHz/16MHz, 且具有快速起震、抗干擾能力強及功耗低的特性。HAO 輸出頻率值具有可校正性,用戶可通 過軟件的方式對 HAO 的輸出頻率進行校正。

#### 使用內部晶振需要注意事項:

- 使用 HAO 16MHz 晶振時,晶片工作電壓須限制在高壓動作。

- 設置寄存器 HAOTR 0x40304[7:0]的值,可調整 HAO 輸出頻率值。 舉例:當設定 HAO 工作在 2MHz 時,如果實際輸出只有 1.99MHz,那麼即可藉由調整控制位 HAOTR[7:0]來調整頻率輸出,HAOTR 預設值為 0x80,往上調整即可增加 HAO 實際工作頻率。

- 晶片在默認啟動的震盪器為內部 HAO 2MHz,用戶可進行設置暫存器 0x40300[4:3]來配置為其它的 HAO 輸出頻率值。

- HAO 配置為 4MHz 起震的穩定時間約為 0.5ms。

- 執行休眠(SLEEP)指令後,HAO 震盪器皆會停止震盪進入休眠狀態。

- 從休眠模式(Sleep Mode)到喚醒的時間約 1024\*HAO+2048\*LPO=< 64ms。

注意:如果要滿足上述描述喚醒時間,應該在進入 Sleep Mode 之前,CPU 頻率源選擇為

HAO。

- 執行待機(IDLE)指令,並不會停止 HAO 震盪器,但 CPU 會進入待機狀態。

- 從 Idle Mode 到喚醒時間約 500 個指令週期,當 CPU Clock 使用預設 HAO=2MHz 時, 喚醒時間約 250us。

LPO 為晶片內部低速 RC 震盪器·輸出頻率 35KHz·具有低功耗電流特性·且在晶片上電或喚醒後即起振·同時也是無法關閉·在整個晶片工作過程 LPO 都是運行的。

- LPO 起振穩定時間約為 510us 且是看門狗(WDT)的唯一工作時脈源。

- 執行休眠指令(SLEEP)後, LPO 震盪器皆會停止震盪。

- 執行待機指令(IDLE)後, LPO 不會停止震盪,但 CPU 會進入待機狀態。

- 從 Idle Mode 到喚醒時間約 500 個指令週期,當 CPU Clock 使用預設 LPO=35kHz 時, 喚醒時間約 14ms。

典型的 HAO 與 LPO 輸出頻率值如下表 6-2 所示。

UG-HY16F3981-V07\_TC

| 符號      | 頻率                                     |          | 頻率源配置       | 指令執行狀態  |       |      |

|---------|----------------------------------------|----------|-------------|---------|-------|------|

| חווכ הו | // // // // // // // // // // // // // | ENHAO[1] | HAO[1:0]    | CKHS[1] | Sleep | Idle |

|         | 2MHz                                   | 1        | 00B         | 0       | 停止    | 可動作  |

| HAO     | 4MHz                                   | 1        | 01B         | 0       | 停止    | 可動作  |

| ПАО     | 10MHz                                  | 1        | 10B         | 0       | 停止    | 可動作  |

|         | 16MHz                                  | 1        | 11B         | 0       | 停止    | 可動作  |

| LPO     | 35KHz                                  | 晶片上電     | <b>『後起振</b> | CKLS=0  | 停止    | 震盪   |

表 6-2 內部晶振配置

#### HAO 內部頻率校正使用說明:

晶片 HAO 內部頻率出廠時候會有+/-10%左右的誤差,如果使用者想要有更精確的 HAO 工作頻率,可以使用 HAO 頻率校正功能。 HAO 頻率校正部份,可以使用紘康 C 函式庫 DrvCLOCK\_CalibrateHAO 這個函數,可以透過這個函數的設定,控制 HAO 震盪頻率誤差範 圍接近在+/-2%以內,詳細正確 HAO 頻率規格,可以參考文件 DS-HY16F3981\_TC 說明,函數使用說明可以參考如下:

#### - | 派數

void DrvCLOCK\_CalibrateHAO(short int uMHZ)

-函數功能

按照晶片出廠時 HAO 的校正值來校正內部晶振(HAO);使用時注意要與選定的 HAO 頻率對應; 設置暫存器 0x40304[7:0]的值

-輸入參數

uMHZ [in]待校正值的 HAO 頻率模式選擇

0:校正 2MHZ; 1:校正 4MHZ; 2:校正 10MHZ; 3:校正 16MHZ;

#### 6.1.3. 工作頻率源配置

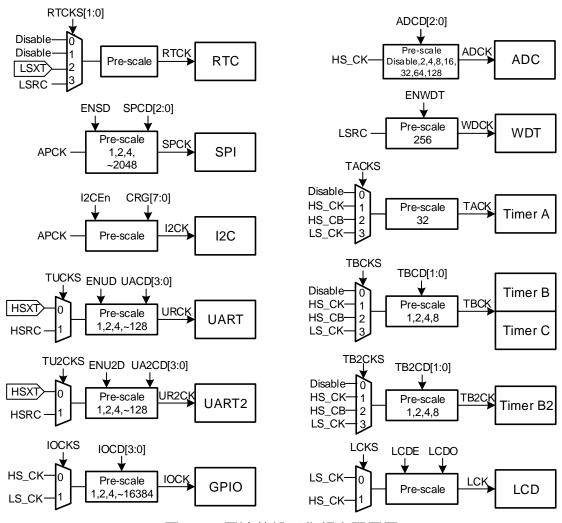

內部外部震盪器都可以為 CPU 提供頻率源,頻率源經過除頻器後供給 CPU。晶片可透過頻率選擇器 MCUCKS[1]選擇 CPU 的頻率源為 HS\_CK 或 LS\_CK·通過除頻器 ENMCD[1] 對頻率源進行除頻。因而 CPU 的工作頻率模式有多種可選擇,進而決定晶片的指令週期。周邊外設工作頻率源同樣由外部或內部震盪器透過 HS\_CK 或 LS\_CK 經過除頻器供給。或者由震盪器直接供給頻率源,如 WDT。由於周邊外設工作性質不同而有不同的規劃,使用者可參考下圖說明。

UG-HY16F3981-V07\_TC

圖 6-1 CPU 工作頻率源配置圖

圖 6-2 周邊外設工作頻率配置圖

© 2016-2021 HYCON Technology Corp

UG-HY16F3981-V07\_TC

#### 6.2. 暫存器位址

| Clock Register Address            | 31  | 24  | 23 | 16 | 15  | 8   | 7  | 0   |

|-----------------------------------|-----|-----|----|----|-----|-----|----|-----|

| CLK Base Address + 0X00 (0X40300) | -   |     | -  |    | MA: | SK0 | RI | EG0 |

| CLK Base Address + 0X04 (0X40304) | -   |     | -  |    |     | -   | HA | OTR |

| CLK Base Address + 0X08 (0X40308) | MAS | SK1 | RE | G1 | MA: | SK2 | RI | EG2 |

| CLK Base Address + 0X0C (0X4030C) | MAS | SK3 | RE | G3 | MA: | SK4 | RI | EG4 |

| CLK Base Address + 0X10 (0X40310) | MAS | SK5 | RE | G5 | MA: | SK6 | RI | EG6 |

| CLK Base Address + 0X14 (0X40314) | -   |     | -  |    | MA: | SK7 | RI | EG7 |

<sup>-</sup>保留

#### 6.3. 暫存器功能

## 6.3.1. 時脈系統暫存器 CLKCR0

|        | Clock Base Address + 0x00 (0x40300) |                                             |      |             |              |     |     |      |  |

|--------|-------------------------------------|---------------------------------------------|------|-------------|--------------|-----|-----|------|--|

| Symbol |                                     |                                             | CLK0 | (Clock Cont | rol Register | 0)  |     |      |  |

| Bit    |                                     |                                             |      | [31:16      | 6]           |     |     |      |  |

| 名稱     |                                     | Rsv                                         |      |             |              |     |     |      |  |

| RW     |                                     |                                             |      | R-0         |              |     |     |      |  |

| Bit    | [15:8]                              | [7]                                         | [6]  | [5]         | [4:3]        | [2] | [1] | [0]  |  |

| 名稱     | MASK                                | MASK OHS_HS CKLS CKHS HAO ENOLS ENOHS ENHAO |      |             |              |     |     |      |  |

| RW     | R0W-0                               |                                             |      | RV          | V-0          |     |     | RW-1 |  |

| 位元       | 名稱            | 描述   |                   |

|----------|---------------|------|-------------------|

|          |               | 外部震  | 温器模式選擇            |

| Bit[07]  | OHS_HS        | 0    | HSXT<4MHz         |

|          |               | 1    | HSXT>4MHz         |

|          |               | 晶片但  | 速頻率源選擇            |

| Bit[06]  | CKLS          | 0    | 內部低速震盪器(OSC_LSRC) |

|          |               | 1    | 外部低速振盪器(OSC_LSXT) |

|          |               | 晶片高  | 速頻率源選擇            |

| Bit[05]  | CKHS          | 0    | 內部高速振盪器(OSC_HSRC) |

|          |               | 1    | 外部高速振盪器(OSC_HSXT) |

|          |               | 內部高  | 速振盪器頻率模式設置        |

| D        |               | [00] | 2MHz              |

| Bit[4~3] | HAO           | [01] | 4MHz              |

|          |               | [10] | 10MHz             |

|          |               | [11] | 16MHz             |

|          |               | 外部但  | 速震盪器開啟控制          |

| Bit[02]  | Bit[02] ENOLS | 0    | 關閉                |

|          |               | 1    | 開啟                |

| Bit[01]  | ENOHS         | 外部高  | 速振盪器開啟控制          |

| Dit[O1]  | LINOING       | 0    | 關閉                |

© 2016-2021 HYCON Technology Corp

UG-HY16F3981-V07\_TC

www.hycontek.com page31

|         |               | 1 | 開啟       |

|---------|---------------|---|----------|

|         | Bit[00] ENHAO |   | 速振盪器開啟控制 |

| Bit[00] |               |   | 關閉       |

|         |               | 1 | 開啟       |

#### 注意事項:

HS\_CK、LS\_CK 時脈源切換防呆控制:利用 CKHS 或 CKLS 切換 HS\_CK 或 LS\_CK 的時脈源時,會判讀相對應的振盪器是否開啟,如未開啟將不執行切換動作。

#### 注意事項:

振盪器關閉防呆控制:如欲關閉某振盪器時,需先將 HS\_CK 或 LS\_CK 切換至另一組已開 啟

之振盪器,避免振盪器關閉後使系統無時脈源而當機。

#### 注意事項:

高速振盪器關閉防呆控制:兩組高速振盪可以同時關閉而不受前項防呆機制限制,但是需先將 CPU Core 時脈源切換至低速時脈源,否則無法同時關閉兩組高速振盪器。

#### 6.3.2. 時脈系統暫存器 CLKCR1

|        | Clock Base Address + 0X04 (0X40304) |         |  |  |  |  |  |  |  |

|--------|-------------------------------------|---------|--|--|--|--|--|--|--|

| Symbol | CLKCR1 (Clock Control Register 1)   |         |  |  |  |  |  |  |  |

| Bit    | [31:16]                             |         |  |  |  |  |  |  |  |

| 名稱     | Reserved                            |         |  |  |  |  |  |  |  |

| RW     | R-0                                 |         |  |  |  |  |  |  |  |

| Bit    | [15:8]                              | [7:0]   |  |  |  |  |  |  |  |

| 名稱     | Reserved                            | HAOTR   |  |  |  |  |  |  |  |

| RW     | R-0                                 | RW-0X80 |  |  |  |  |  |  |  |

| 位元       | 名稱    | 描述  | 苗述          |  |  |  |  |

|----------|-------|-----|-------------|--|--|--|--|

|          | HAOTR | 內部高 | 速震盪器校正控制寄存器 |  |  |  |  |

| Bit[7:0] |       | 0   | 設置 0        |  |  |  |  |

|          |       | 1   | 設置 1        |  |  |  |  |

1\*LSB.Step = 0.125%

0000\_0000 是最慢速度

1000\_0000 是預設速度

1111 1111 為最快速度

說明:HAO 頻率校正部份,可以使用紘康 C 函式庫 DrvCLOCK\_CalibrateHAO 這個函數,可以透過這個函數的設定,把各頻段 HAO 的 Trim 值填入在 HAOTR 暫存器, 可控制 HAO 震盪頻率誤差範圍接近在+/-2%以內

## 6.3.3. 時脈系統暫存器 CLKCR2

|        | Clock Base Address + 0x08 (0x40308) |             |            |      |      |         |       |        |

|--------|-------------------------------------|-------------|------------|------|------|---------|-------|--------|

| Symbol | CLKCR2 (Clock Control Register 2)   |             |            |      |      |         |       |        |

| Bit    | [31:24]                             | [23:22]     | [21]       | [20] | [19] | [18:16] |       |        |

| 名稱     | MASK                                | RTCKS       | TUCKS      | ENUD | Rsv  | UACD    |       |        |

| RW     | R0W-0                               | RW-0        | RW-0 R-0   |      |      | RW-0    |       |        |

| Bit    | [15:08]                             | [7:6] [5:4] |            | [3   | :2]  | [1]     | [0]   |        |

| 名稱     | MASK                                | TBCKS       | TBCKS TBCD |      | TAG  | CKS     | ENMCD | MCUCKS |

| RW     | R0W-0                               | RW-0        |            |      |      |         |       |        |

| 位元         | 名稱    | 描述                             |  |  |  |  |  |

|------------|-------|--------------------------------|--|--|--|--|--|

|            | RTCKS | RTC 時脈源選擇                      |  |  |  |  |  |

|            |       | 00 關閉                          |  |  |  |  |  |

| Bit[23~22] |       | 01 關閉                          |  |  |  |  |  |

|            |       | 10 LSXT(LSXT 需致能·否則視為 Disable) |  |  |  |  |  |

|            |       | 11 LPO                         |  |  |  |  |  |

|            |       | EUART 時脈源選擇                    |  |  |  |  |  |

| Bit[21]    | TUCKS | 0 HSXT: 外部高速震盪器                |  |  |  |  |  |

|            |       | 1 HSRC: 內部高速震盪器                |  |  |  |  |  |

|            |       | EUART 時脈源開啟控制                  |  |  |  |  |  |

| Bit[20]    | ENUD  | 0 關閉                           |  |  |  |  |  |

|            |       | 1 開啟                           |  |  |  |  |  |

|            |       | EUART 時脈源 除頻設置                 |  |  |  |  |  |

|            | UACD  | 0000 EUART 時脈源/ 1              |  |  |  |  |  |

|            |       | 0001 EUART 時脈源/ 2              |  |  |  |  |  |

|            |       | 0010 EUART 時脈源/ 4              |  |  |  |  |  |

| Bit[18~16] |       | 0011 EUART 時脈源/ 8              |  |  |  |  |  |

|            |       | 0100 EUART 時脈源/ 16             |  |  |  |  |  |

|            |       | 0101 EUART 時脈源/ 32             |  |  |  |  |  |

|            |       | 0110 EUART 時脈源/ 64             |  |  |  |  |  |

|            |       | 0111 EUART 時脈源/ 128            |  |  |  |  |  |

|            |       | Timer B,C 時脈源選擇                |  |  |  |  |  |

| D:4[7 0]   | TDOVO | 00 關閉                          |  |  |  |  |  |

| Bit[7~6]   | TBCKS | 01 HS_CK                       |  |  |  |  |  |

|            |       | 10 HS_CB<br>11 LS_CK           |  |  |  |  |  |

|            |       | Timer B,C 時脈除頻設置               |  |  |  |  |  |

| D'45 43    | TDOD  | 00  TBCK/1                     |  |  |  |  |  |

| Bit[5~4]   | TBCD  | 01 TBCK/2                      |  |  |  |  |  |

|            |       | 10 TBCK/4<br>11 TBCK/8         |  |  |  |  |  |

|            |       |                                |  |  |  |  |  |

© 2016-2021 HYCON Technology Corp

UG-HY16F3981-V07\_TC

## 21-bit ENOB ΣΔADC, 32-bit MCU & 64KB Flash

|          | TACKS  | Timer A 時脈源選擇, 除頻器固定為 1/32                         |

|----------|--------|----------------------------------------------------|

|          |        | 0 關閉                                               |

| Bit[3~2] |        | 1 HS_CK                                            |

|          |        | 2 HS_CB (如果 CPU 以 HAO 為時脈源, TMA 則以 HSXT 為時脈, 反之亦然) |

|          |        | 3 LS_CK                                            |

|          | ENMCD  | MCU 輸入時脈除頻設置                                       |

| Bit[01]  |        | 0 MCU Clock/1                                      |

|          |        | 1 MCU Clock/2                                      |

|          |        | MCU 輸入時脈源選擇                                        |

| Bit[00]  | MCUCKS | 0 HS_CK                                            |

|          |        | 1 LS_CK                                            |

UG-HY16F3981-V07\_TC

## 6.3.4. 時脈系統暫存器 CLKCR3

| Clock Base Address + 0x0C (0x4030C) |        |      |      |      |       |  |  |  |

|-------------------------------------|--------|------|------|------|-------|--|--|--|

| CLKCR3 (Clock Control Register 3)   |        |      |      |      |       |  |  |  |

| [31:24] [23:21] [20] [19:16]        |        |      |      |      |       |  |  |  |

| MASK                                | MASK - |      | IOCD |      |       |  |  |  |

| R0W-0                               | -      | RW-0 |      |      |       |  |  |  |

| [15:08]                             | [7]    | [6:4 | 4]   | [3]  | [2:0] |  |  |  |

| MASK                                | -      | ADCD |      | ENSD | SPCD  |  |  |  |

| R0W-0                               | R-0    |      | R    | 2W-0 |       |  |  |  |

| 位元         | 名稱    | 描述                                 |  |  |  |  |  |

|------------|-------|------------------------------------|--|--|--|--|--|

|            | IOCKS | GPIO 輸入時脈源選擇                       |  |  |  |  |  |

| Bit[20]    |       | 0 HS_CK                            |  |  |  |  |  |

|            |       | 1 LS_CK                            |  |  |  |  |  |

|            |       | GPIO 時脈除頻器設置                       |  |  |  |  |  |

|            |       | 0000 關閉                            |  |  |  |  |  |

|            |       | 0001 GPIO 時脈源/ 1                   |  |  |  |  |  |

|            |       | 0010 GPIO 時脈源/ 2                   |  |  |  |  |  |

|            |       | 0011 GPIO 時脈源/ 4                   |  |  |  |  |  |

|            |       | 0100 GPIO 時脈源/ 8                   |  |  |  |  |  |

|            |       | 0101 GPIO 時脈源/ 16                  |  |  |  |  |  |

|            |       | 0110 GPIO 時脈源/ 32                  |  |  |  |  |  |

| Bit[19:16] | IOCD  | 0111 GPIO 時脈源/ 64                  |  |  |  |  |  |

|            |       | 1000 GPIO 時脈源/ 128                 |  |  |  |  |  |

|            |       | 1001 GPIO 時脈源/ 256                 |  |  |  |  |  |

|            |       | 1010 GPIO 時脈源/ 512                 |  |  |  |  |  |

|            |       | 1011 GPIO 時脈源/ 1024                |  |  |  |  |  |

|            |       | 1100 GPIO 時脈源/ 2048                |  |  |  |  |  |

|            |       | 1101 GPIO 時脈源/ 4096                |  |  |  |  |  |

|            |       | 1110 GPIO 時脈源/ 8192                |  |  |  |  |  |

|            |       | 1111 GPIO 時脈源/ 16384               |  |  |  |  |  |

|            |       | ADC 時脈除頻器設置                        |  |  |  |  |  |

|            |       | 000 Disable                        |  |  |  |  |  |

|            |       | 001 Reserved                       |  |  |  |  |  |

| Bit[6~4]   | ADCD  | 010 ~HS_CK / 4                     |  |  |  |  |  |

|            | ADCD  | 011 ~HS_CK / 8<br>100 ~HS_CK / 16  |  |  |  |  |  |

|            |       | 100 ~HS_CK / 16<br>101 ~HS_CK / 32 |  |  |  |  |  |

|            |       | 110 ~HS_CK / 64                    |  |  |  |  |  |

|            |       | 111 ~HS_CK / 128                   |  |  |  |  |  |

|            |       | SPI 時脈開關                           |  |  |  |  |  |

| Bit[03]    | ENSD  | 0 關閉                               |  |  |  |  |  |

|            |       | 1 開啟                               |  |  |  |  |  |

|            |       |                                    |  |  |  |  |  |

UG-HY16F3981-V07\_TC

|          | SPCD | SPI 限 | ·<br>·<br>·<br>·<br>·<br>·<br>·<br>·<br>·<br>·<br>·<br>·<br>·<br>· |

|----------|------|-------|--------------------------------------------------------------------|

|          |      | 000   | Reserved                                                           |

|          |      | 001   | SPI 時脈源/ 2                                                         |

|          |      | 010   | SPI 時脈源/ 4                                                         |

| Bit[2~0] |      | 011   | SPI 時脈源/ 8                                                         |

|          |      | 100   | SPI 時脈源/ 32                                                        |

|          |      | 101   | SPI 時脈源/ 128                                                       |

|          |      | 110   | SPI 時脈源/ 512                                                       |

|          |      | 111   | SPI 時脈源/ 2048                                                      |

註:在設置 ADCD 的 ADC 時脈除頻器時,最佳的 ADC 工作脈頻率為 1MHz 建議設置 HS\_CK=4MHz,讓 ADCD 工作頻率為 HS\_CK / 4=1MHz.

#### 6.3.5. 時脈系統暫存器 CLKCR4

| Clock Base Address + 0x10 (0x40310) |                                   |         |        |       |       |         |  |  |

|-------------------------------------|-----------------------------------|---------|--------|-------|-------|---------|--|--|

| Symbol                              | CLKCR4 (Clock Control Register 4) |         |        |       |       |         |  |  |

| Bit                                 | [31:24]                           | [23:22] | [21]   | [20]  | [19]  | [18:16] |  |  |

| 名稱                                  | MASK                              | LCDCPD  | UT2CKS | ENU2D | -     | UA2CD   |  |  |

| RW                                  | R0W-0                             |         | RW-0   |       | -     | RW-0    |  |  |

| Bit                                 | [15:08]                           | [7]     | [6:4]  |       | [3:1] | [0]     |  |  |

| 名稱                                  | MASK                              | -       | LCDO   |       | LCDE  | LCKS    |  |  |

| RW                                  | R0W-0                             | -       |        |       | RW-0  |         |  |  |

| 位元         | 名稱     | 描述  |                                                  |  |  |  |

|------------|--------|-----|--------------------------------------------------|--|--|--|

|            |        | LC  | )電荷泵調器時脈源選擇 (這是設置 LCD internal charge pump 掃描頻率, |  |  |  |

|            |        | 可依  | 家實際顯示效果及功耗來做不同類型選用)                              |  |  |  |

| Di+[22-22] | LCDCPD | 0   | LS_CK / 1 or HS_CK/8 (LS_CK 或 HS_CK 由 LCKS 決定)   |  |  |  |

| Bit[22:23] | LCDCPD | 1   | LS_CK / 2 or HS_CK/16 (LS_CK 或 HS_CK 由 LCKS 決定)  |  |  |  |

|            |        | 2   | LS_CK / 4 or HS_CK/32 (LS_CK 或 HS_CK 由 LCKS 決定)  |  |  |  |

|            |        | 3   | LS_CK / 4 or HS_CK/32 (LS_CK 或 HS_CK 由 LCKS 決定)  |  |  |  |

|            | UT2CKS | UAF | UART2 時脈源選擇                                      |  |  |  |

| Bit[21]    |        | 0   | HSXT: 外部高速震盪器                                    |  |  |  |

|            |        | 1   | HSRC: 內部高速震盪器                                    |  |  |  |

|            | ENUD2D | UAF | RT2 時脈源開啟控制                                      |  |  |  |

| Bit[20]    |        | 0   | 關閉                                               |  |  |  |

|            |        | 1   | 開啟                                               |  |  |  |

|            | UA2CD  | UAF | RT2 時脈源除頻設置                                      |  |  |  |

| Bit[18:16] |        | 0   | UART2 時脈源/ 1                                     |  |  |  |

| Dit[10.10] |        | 1   | UART2 時脈源/ 2                                     |  |  |  |

|            |        | 2   | UART2 時脈源/ 4                                     |  |  |  |

© 2016-2021 HYCON Technology Corp

UG-HY16F3981-V07\_TC

| 位元       | 名稱   | 描述  | Ì              |

|----------|------|-----|----------------|

|          |      | 3   | UART2 時脈源/ 8   |

|          |      | 4   | UART2 時脈源/ 16  |

|          |      | 5   | UART2 時脈源/ 32  |

|          |      | 6   | UART2 時脈源/ 64  |

|          |      | 7   | UART2 時脈源/ 128 |

|          |      | LCD | D 時脈源 2 階除頻器設置 |

|          |      | 0   | LCD 時脈源/ 1     |

|          |      | 1   | LCD 時脈源/ 3     |

|          |      | 2   | LCD 時脈源/ 5     |

| Bit[6~4] | LCDO | 3   | LCD 時脈源/ 7     |

|          |      | 4   | LCD 時脈源/ 9     |

|          |      | 5   | LCD 時脈源/ 11    |

|          |      | 6   | LCD 時脈源/ 13    |

|          |      | 7   | LCD 時脈源/ 15    |

|          |      | LCD | 時脈源 1 階除頻器設置   |

|          |      | 0   | 關閉             |

|          |      | 1   | LCD 時脈源/ 1     |

|          |      | 2   | LCD 時脈源/ 2     |

| Bit[3~1] | LCDE | 3   | LCD 時脈源/ 4     |

|          |      | 4   | LCD 時脈源/ 8     |

|          |      | 5   | LCD 時脈源/ 16    |

|          |      | 6   | LCD 時脈源/ 32    |

|          |      | 7   | 關閉             |

|          |      | LCD | <b>)</b> 時脈源選擇 |

| Bit[00]  | LCKS | 0   | LS_CK(固定÷8)    |

|          |      | 1   | HS_CK(固定÷64)   |

# 6.3.6. 時脈系統暫存器 CLKCR5

|        | Clock Base Address + 0x014 (0x40314) |                 |       |       |  |  |  |  |  |

|--------|--------------------------------------|-----------------|-------|-------|--|--|--|--|--|

| Symbol | CLKCR5 (Clock Co                     | ontrol Register | 4)    |       |  |  |  |  |  |

| Bit    | [31:16]                              |                 |       |       |  |  |  |  |  |

| 名稱     | Reserved                             |                 |       |       |  |  |  |  |  |

| RW     | R-                                   | 0               |       |       |  |  |  |  |  |

| Bit    | [15:8]                               | [7:6]           | [5:4] | [3:0] |  |  |  |  |  |

| 名稱     | MASK                                 | TB2CKS          | TM2CD | -     |  |  |  |  |  |

| RW     | R0W-0                                | RW              | /-0   | -     |  |  |  |  |  |

UG-HY16F3981-V07\_TC

# HY16F3981 User's Guide

# 21-bit ENOB ΣΔADC, 32-bit MCU & 64KB Flash

4 X 32~6 X 30 LCD Driver

| 位元       | 名稱     | 描述    |                 |

|----------|--------|-------|-----------------|

|          |        | Timer | B2 時脈源選擇        |

| D:4[7 C] | TMOCKS | 0     | 關閉              |

| Bit[7~6] | TM2CKS | 1     | HS_CK           |

|          |        | 2     | HS_CB           |

|          |        | 3     | LS_CK           |

|          |        | Timer | B2 時脈源除頻設置      |

|          |        | 0     | Timer B2 時脈源/ 1 |

| Bit[5~4] | TM2CD  | 1     | Timer B2 時脈源/ 2 |

|          |        | 2     | Timer B2 時脈源/ 4 |

|          |        | 3     | Timer B2 時脈源/ 8 |

UG-HY16F3981-V07\_TC

### 7. 中斷控制系統

#### 7.1. 整體總說明

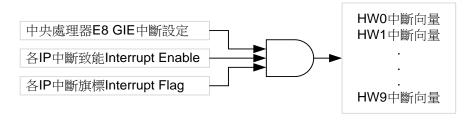

中斷向量與中斷優先權說明:

這個中斷模塊包含中斷啟動控制器、中斷使能控制器和中斷事件旗標暫存器,用於管理整體的中斷服務,如通訊功能中斷、定時器中斷、ADC中斷、IO外部中斷。

晶片提供 9 級中斷源,同時也提供 4 級中斷響應優先權級別,也就是中斷 HW0~HW9 中斷向量函數響應的優先順序,如果當中斷響應優先權級別都設置相同的時候,則中斷響應優先權從高位到低位為 HW0、HW1 到 HW9。中斷服務由中斷事件旗標(INTF),中斷事件服務致能啟動(INTE)與中斷總控制 GIE 和向量位址 HW0~HW9 組成。當中斷事件成立之後,則程式計數器 PC 在下一個指令週期會指向程式記憶體的中斷服務向量位址 HW0~HW9 以執行中斷服務程式。

圖 7-1 中斷服務架構圖

| Interrupt Vector Address                         | Vector | Interrupt Function |

|--------------------------------------------------|--------|--------------------|

| INT Base Address + 0x00 (I2C/UART/SPI 通訊介面)      | HW0    | void HW0_ISR(void) |

| INT Base Address + 0x04 (Timer ABC /WDT/ HW RTC) | HW1    | void HW1_ISR(void) |

| INT Base Address + 0x08 (ADC)                    | HW2    | void HW2_ISR(void) |

| INT Base Address + 0x0C (OPA)                    | HW9    | void HW9_ISR(void) |

| INT Base Address + 0x10 (PT3)                    | HW4    | void HW4_ISR(void) |

| INT Base Address + 0x14 (PT2)                    | HW5    | void HW5_ISR(void) |

| INT Base Address + 0x18 (UART2)                  | HW7    | void HW7_ISR(void) |

| INT Base Address + 0x1C (TMB2)                   | HW8    | void HW8_ISR(void) |

注意:INT HW6 是屬於 SW INT

中斷群組 HW0~HW9 具有優先權可以設定,提供 4 種優先權等級(0~3)。

- 0:優先權級別為最高級別

- 1:優先權級別為次高級別

- 2:優先權級別為低級級別

- 3:優先權級別為最低級別

系統預設 HW0~HW9 都設定為級別 0(優先權級別為最高級別)。

© 2016-2021 HYCON Technology Corp

UG-HY16F3981-V07\_TC

www.hycontek.com page39

當優先權級別都設定為相同時候,則優先權為 HW0>HW1>HW2...>HW9。

#### 舉例說明:

設定 HWO 的優先權為級別 1·HW1 的優先權為級別 0·當兩中斷同時發生的時候,此時會因為優先權級別的設定關係·先進入 HW1 中斷。如果設定 HWO 的優先權為級別 0·HW1 的優先權也為級別 0·當兩中斷同時發生的時候,此時兩中斷級別雖然設定相同,但是會優先進入 HWO 中斷。

#### 操作細節說明:

用戶置 1 或清 0 相對應中斷使能位元,可實現開啟或關閉相應的中斷功能,寫 1 可以開啟中斷功能。中斷事件發生後,會生產中斷旗標,使用者可自行清零旗標以便取消中斷請求。必須開啟全局中斷使能位元 GIE=1,否則無法響應任何中斷。中斷向量優先權決定在多個中斷請求同時發生時,需先響應中斷優先權高的中斷向量。當進入中斷向量服務程式,高級的中斷向量可以終止當前中斷服務轉去執行高級中斷服務。注意,當進入中斷向量服務程式中,GIE 會自動被置為 0,所以需要先把 GIE 置為 1,滿足高級中斷服務條件成立即可進入高級中斷服務程式,當高級中斷服務執行完,程式會回到原本的中斷服務程式,繼續往下執行程式。晶片中斷對應的中斷向量程式入口位址如下表

#### 7.2. 暫存器位址

| Interrupt Register Address                   | 31 24  | 23 16 | 15 8   | 7 0   |

|----------------------------------------------|--------|-------|--------|-------|

| INT Base Address + 0x00 (INTCOM) (0x40000)   | MASK0  | REG0  | MASK1  | REG1  |

| INT Base Address + 0x04 (INTTMR) (0x40004)   | MASK2  | REG2  | MASK3  | REG3  |

| INT Base Address + 0x08 (INTADC) (0x40008)   | MASK4  | REG4  | MASK5  | REG5  |

| INT Base Address + 0x0C (INTOPA) (0x4000C)   | MASK6  | REG6  | MASK7  | REG7  |

| INT Base Address + 0x10 (INTPT3) (0x40010)   | MASK8  | REG8  | MASK9  | REG9  |

| INT Base Address + 0x14 (INTPT2) (0x40014)   | MASK10 | REG10 | MASK11 | REG11 |

| INT Base Address + 0x18 (INTUART2) (0x40018) | MASK12 | REG12 | MASK13 | REG13 |

| INT Base Address + 0x1C (INTTMB2) (0x4001C)  | MASK14 | REG14 | MASK15 | REG15 |

#### 7.3. 暫存器功能

#### 7.3.1. 中斷控制暫存器 INTCOM

| INT Bas | INT Base Address + 0x00 (0x40000) |        |       |         |       |        |         |         |         |           |       |       |       |       |

|---------|-----------------------------------|--------|-------|---------|-------|--------|---------|---------|---------|-----------|-------|-------|-------|-------|

| Symbol  |                                   |        |       |         | INTC  | OM (In | terrupt | Control | Registe | r 0)      |       |       |       |       |

| Bit     |                                   |        |       | [31:24] |       |        |         | [23:22] | [21]    | [20]      | [19]  | [18]  | [17]  | [16]  |

| 名稱      |                                   |        |       | MASK    |       |        |         | -       | I2CEIE  | I2CIE     | UTxIE | URxIE | STxIE | SRxIE |

| RW      |                                   |        |       | R0W-0   |       |        |         | -       | RW-0    |           |       |       |       |       |

| Bit     | [15:14]                           | [13]   | [12]  | [11]    | [10]  | [09]   | [80]    | [07:06] | [05]    | [04]      | [03]  | [02]  | [01]  | [00]  |

| 夕顿      |                                   |        |       | MASK    |       |        |         |         |         | EIF I2CIF |       |       | OTIE  | CDVIC |

| 名稱      | -                                 | I2CEIR | I2CIR | UTxIR   | URxIR | STxIR  | SRxIR   | -       | IZCEIF  | IZCIF     | UIXIF | UKXIF | SIXIF | SKXIF |

© 2016-2021 HYCON Technology Corp

UG-HY16F3981-V07\_TC

# HY16F3981 User's Guide 21-bit ENOB ΣΔADC, 32-bit MCU & 64KB Flash 4×32~6×30 LCD Driver

| RW | R-0 | - | RW0-0 |

|----|-----|---|-------|

|    |     |   |       |

(對暫存器寫時 Bit15~8 為 MASK,對暫存器讀時 Bit15~8 為一般暫存器)

| 位元       | 名稱            | 描述                      |

|----------|---------------|-------------------------|

|          |               | I2C 錯誤中斷致能控制            |

| Bit[21]  | I2CEIE        | 0 關閉                    |

|          |               | 1 開啟                    |

|          |               | I2C 中斷致能控制              |

| Bit[20]  | I2CIE         | 0 關閉                    |

|          |               | 1 開啟                    |

|          |               | UART 發送(TX)中斷致能控制       |

| Bit[19]  | UTxIE         | 0 關閉                    |

|          |               | 1 開啟                    |

|          |               | UART 接收(RX)中斷致能控制       |

| Bit[18]  | URxIE         | 0 關閉                    |

|          |               | 1 開啟                    |

|          |               | SPI 發送(TX)中斷致能控制        |

| Bit[17]  | STxIE         | 0 關閉                    |

|          |               | 1 開啟                    |

| D:4[4 C] | SRxIE         | SPI 接收(RX)中斷致能控制        |

| Bit[16]  | SKXIE         | 0     關閉       1     開啟 |

|          |               | 1   開啟                  |

| Bit[13]  | I2CEIR        | I                       |

| Dit[10]  | IZCEIR        | 1 中斷                    |

|          |               | I2C 中斷請求                |

| Bit[12]  | I2CIR         | 0 正常                    |

| ' '      | _             | 1 中斷                    |

|          |               | UART TX 中斷請求            |

| Bit[11]  | UTxIR         | 0 正常                    |

|          |               | 1 中斷                    |

|          |               | UART RX 中斷請求            |

| Bit[10]  | Bit[10] URxIR | 0 正常                    |

|          |               | 1 中斷                    |

| Dit[00]  | STxIR         | SPITX 中斷請求              |

| Bit[09]  | SIXIK         | 0 正常                    |

© 2016-2021 HYCON Technology Corp

UG-HY16F3981-V07\_TC

| 位元      | 名稱     | 描述                    |

|---------|--------|-----------------------|

|         |        | 1 中斷                  |

|         |        | SPI RX 中斷請求           |

| Bit[08] | SRxIR  | 0 正常                  |

|         |        | 1 中斷                  |

|         |        | I2C 錯誤中斷旗標(準位觸發)      |

| Bit[05] | I2CEIF | 0 正常                  |

|         |        | 1 I2C 錯誤發生中斷          |

|         |        | I2C 中斷旗標(準位觸發)        |

| Bit[04] | I2CIF  | 0 正常                  |

|         |        | 1 I2C 發生中斷            |

|         |        | UART 發送(TX)中斷旗標(準位觸發) |

| Bit[03] | UTxIF  | 0 正常                  |

|         |        | 1 UART 發送(TX)發生中斷     |

|         |        | UART 接收(RX)中斷旗標(準位觸發) |

| Bit[02] | URxIF  | 0 正常                  |

|         |        | 1 UART 接收(RX)發生中斷     |

|         |        | SPI 發送(TX)中斷旗標(準位觸發)  |

| Bit[01] | STxIF  | 0 正常                  |

|         |        | 1 SPI 發送(TX)發生中斷      |

|         |        | SPI 接收(RX)中斷旗標(準位觸發)  |

| Bit[00] | SRxIF  | 0 正常                  |

|         |        | 1 SPI 接收(RX)發生中斷      |

## 7.3.2. 中斷控制暫存器 INTTMR

|        | INT Base Address + 0x04 (0x40004) |       |       |         |        |         |        |         |       |        |          |          |         |         |

|--------|-----------------------------------|-------|-------|---------|--------|---------|--------|---------|-------|--------|----------|----------|---------|---------|

| Symbol |                                   |       |       |         | INTT   | MR (Int | errupt | Control | Regis | ter 1) |          |          |         |         |

| Bit    |                                   |       |       | [31:24] |        |         |        | [23:22] | [21]  | [20]   | [19]     | [18]     | [17]    | [16]    |

| 名稱     |                                   |       |       | MASK    |        |         |        | -       | RTCIE | WDTIE  | TMC1IE   | TMC0IE   | TMBIE   | TMAIE   |

| RW     |                                   |       |       | R0W-0   |        |         |        | -       | RW-0  |        |          |          |         |         |

| Bit    | [15:14]                           | [13]  | [12]  | [11]    | [10]   | [09]    | [08]   | [07:06] | [05]  | [04]   | [03]     | [02]     | [01]    | [00]    |

| 名稱     |                                   | MASK  |       |         |        |         |        |         | RTCIF | WDTIF  | TMC1IF   | TMC0IF   | TMBIF   | TMAIF   |

| 101件   | -                                 | RTCIR | WDTIR | TMC1IR  | TMC0IR | TMBIR   | TMAIR  | -       | KICII | WDIII  | TIVICTII | TIVICOII | TIVIDII | IIVIAII |

| RW     | R0W-0                             |       |       |         |        |         |        | -       |       |        | RW       | 0-0      |         |         |

(對暫存器寫時 Bit15~8 為 MASK,對暫存器讀時 Bit15~8 為一般暫存器)

| 位元      | 名稱    | 描述              |

|---------|-------|-----------------|

| Bit[21] | RTCIE | 實時時鐘 RTC 中斷致能控制 |

© 2016-2021 HYCON Technology Corp

UG-HY16F3981-V07\_TC

# HY16F3981 User's Guide 21-bit ENOB ΣΔΑDC, 32-bit MCU & 64KB Flash

4 X 32~6 X 30 LCD Driver

| 位元      | 名稱     | 描述                |

|---------|--------|-------------------|

|         |        | 0 關閉              |

|         |        | 1 開啟              |

|         |        | 看門狗(WDT)中斷致能控制    |

| Bit[20] | WDTIE  | 0 關閉              |

|         |        | 1 開啟              |

|         |        | TMC1 中斷致能控制       |

| Bit[19] | TMC1IE | 0 關閉              |

|         |        | 1 開啟              |

|         |        | TMC0 中斷致能控制       |

| Bit[18] | TMC0IE | 0 關閉              |

|         |        | 1 開啟              |

|         |        | 定時計數器 TMB 中斷致能控制  |

| Bit[17] | TMBIE  | 0 關閉              |

|         |        | 1 開啟              |

|         |        | 定時計數器 TMA 中斷致能控制  |

| Bit[16] | TMAIE  | <b>0</b> 關閉       |

|         |        | 1 開啟              |

|         |        | RTC 中斷請求          |

| Bit[13] | RTCIR  | 0 正常              |

|         |        | 1 中斷              |

|         |        | 看門狗中斷請求           |

| Bit[12] | WDTIR  | 0 正常              |

|         |        | 1 中斷              |

|         |        | Timer C 通道 1 中斷請求 |

| Bit[11] | TMC1IR | 0 正常              |

|         |        | 1 中斷              |

|         |        | Timer C 通道 0 中斷請求 |

| Bit[10] | TMC0IR | 0 正常              |

|         |        | 1 中斷              |

|         |        | TMB 中斷請求          |

| Bit[9]  | TMBIR  | 0 正常              |

|         |        | 1 中斷              |

|         |        | TMA 中斷請求          |

| Bit[08] | TMAIR  | 0 正常              |

|         |        | 1 中斷              |

| Bit[05] | RTCIF  | 時鐘 RTC 中斷旗標       |

UG-HY16F3981-V07\_TC

| 位元      | 名稱     | 描述               |

|---------|--------|------------------|

|         |        | 0 正常             |

|         |        | 1 實時時鐘 RTC 發生中斷  |

|         |        | 看門狗(WDT)中斷旗標     |

| Bit[04] | WDTIF  | 0 正常             |

|         |        | 1 看門狗(WDT)發生中斷   |

|         |        | TMC1 中斷旗標        |

| Bit[03] | TMC1IF | 0 正常             |

|         |        | 1 TMC1 發生中斷      |

|         |        | TMC0 中斷旗標        |

| Bit[02] | TMC0IF | 0 正常             |

|         |        | 1 TMC0 發生中斷      |

|         |        | 定時計數器 TMB 中斷旗標   |

| Bit[01] | TMBIF  | 0 正常             |

|         |        | 1 定時計數器 TMB 發生中斷 |

|         |        | 定時計數器 TMA 中斷旗標   |

| Bit[00] | TMAIF  | 0 正常             |

|         |        | 1 定時計數器 TMA 發生中斷 |

# 7.3.3. 中斷控制暫存器 INTADC

|        | INT Base Address + 0x08 (0x40008) |       |                                 |         |  |  |  |  |

|--------|-----------------------------------|-------|---------------------------------|---------|--|--|--|--|

| Symbol |                                   |       | INTADC (Interrupt Control Regis | ster 2) |  |  |  |  |

| Bit    | [31:                              | :24]  | [23:17]                         | [16]    |  |  |  |  |

| 名稱     | MA                                | SK    | Rsv                             | ADCIE   |  |  |  |  |

| RW     | R0\                               | N-0   | R-0                             | RW-0    |  |  |  |  |

| Bit    | [15:9]                            | [8]   | [07:01]                         | [00]    |  |  |  |  |

| 名稱     | Rsv                               | ADCIR | Rsv                             | ADCIF   |  |  |  |  |

| RW     | R                                 | -0    | R-0                             | R-0     |  |  |  |  |

# (對暫存器寫時 Bit15~8 為 MASK,對暫存器讀時 8 為一般暫存器)

| 位元      | 名稱    | 描述          | 描述        |  |  |  |

|---------|-------|-------------|-----------|--|--|--|

|         |       | ADC         | 轉換器中斷致能控制 |  |  |  |

| Bit[16] | ADCIE | 0           | 關閉        |  |  |  |

|         |       | 1           | 開啟        |  |  |  |

|         |       | ADC 中斷請求    |           |  |  |  |

| Bit[08] | ADCIR | 0           | 正常        |  |  |  |

|         |       | 1           | 中斷        |  |  |  |

| Bit[00] | ADCIF | ADC 轉換器中斷旗標 |           |  |  |  |

© 2016-2021 HYCON Technology Corp

UG-HY16F3981-V07\_TC

| 0 | 正常;讀取 ADO(0x41108)時, ADIF 自動清除 |

|---|--------------------------------|

| 1 | ADC 轉換器發生中斷                    |

## 7.3.4. 中斷控制暫存器 INTOPA

|        | INT Base Address + 0x0C (0x4000C) |      |                                   |       |  |  |  |  |

|--------|-----------------------------------|------|-----------------------------------|-------|--|--|--|--|

|        |                                   |      |                                   |       |  |  |  |  |

| Symbol |                                   | INTO | PA (Interrupt Control Register 9) |       |  |  |  |  |

| Bit    | [31:24]                           |      | [23:17]                           | [16]  |  |  |  |  |

| 名稱     | MASK                              |      | Rsv                               | OPOIE |  |  |  |  |

| RW     | R0W-0                             |      | R-0                               | RW-0  |  |  |  |  |

| Bit    | [15:09] [08]                      |      | [07:01]                           | [00]  |  |  |  |  |

|        | MASK                              |      | Boy                               | OPOIF |  |  |  |  |

| 名稱     | Rsv OPOIR                         |      | Rsv                               | OFOIF |  |  |  |  |

| RW     | R-0                               |      | R-0                               | RW0-0 |  |  |  |  |

(對暫存器寫時 Bit15~8 為 MASK,對暫存器讀時 Bit9~8 為一般暫存器)

| 位元        | 名稱    | 描述                  | 描述                                              |  |  |  |  |

|-----------|-------|---------------------|-------------------------------------------------|--|--|--|--|

|           |       | 低雜詞                 | 低雜訊運算放大器輸出(OPO)中斷致能控制                           |  |  |  |  |

| Bit[16]   | OPOIE | 0                   | 關閉                                              |  |  |  |  |

|           |       | 1                   | 開啟                                              |  |  |  |  |

|           |       | 低雜訊運算放大器輸出(OPO)中斷請求 |                                                 |  |  |  |  |

| Bit[08]   | OPOIR | 0                   | 正常                                              |  |  |  |  |

|           |       | 1                   | 中斷                                              |  |  |  |  |

|           |       | 低雜詞                 | R運算放大器輸出(OPO)中斷旗標                               |  |  |  |  |

| Bit[00] O | OPOIF | 0                   | 正常                                              |  |  |  |  |

|           |       | 1                   | 低雜訊運算放大器輸出(OPO)發生中斷(需清除 IP 內 Status 才能清除此 Flag) |  |  |  |  |

© 2016-2021 HYCON Technology Corp

UG-HY16F3981-V07\_TC

# 7.3.5. 中斷控制暫存器 INTPT3

|        | INT Base Address + 0x10 (0x40010) |        |        |              |             |            |        |        |        |

|--------|-----------------------------------|--------|--------|--------------|-------------|------------|--------|--------|--------|

|        |                                   |        |        |              |             |            |        |        |        |

| Symbol |                                   |        | INTF   | PT3 (Interru | ipt Control | Register 4 | )      |        |        |

| Bit    | [31:24]                           | [23]   | [22]   | [21]         | [20]        | [19]       | [18]   | [17]   | [16]   |

|        |                                   |        |        |              |             |            |        |        |        |

| 名稱     | MASK                              | PT37IE | PT36IE | PT35IE       | PT34IE      | PT33IE     | PT32IE | PT31IE | PT30IE |

| RW     | R0W-0                             |        |        |              | RV          | V-0        |        |        |        |

| Bit    | [15:08]                           | [07]   | [06]   | [05]         | [04]        | [03]       | [02]   | [01]   | [00]   |

|        | MASK                              |        |        |              |             |            |        |        |        |

|        |                                   |        |        |              |             |            |        |        |        |

| 名稱     | PT3 IR                            | PT37IF | PT36IF | PT35IF       | PT34IF      | PT33IF     | PT32IF | PT31IF | PT30IF |

| RW     | R-0                               |        |        |              | RW          | /0-0       |        |        |        |

(對暫存器寫時 Bit15~8 為 MASK,對暫存器讀時 Bit15~8 為一般暫存器)

| 位元      | 名稱     | 描述        |               |

|---------|--------|-----------|---------------|

|         |        | PT37IE: F | PT37 外部中斷致能控制 |

| Bit[23] | PT37IE | 0         | 關閉            |

|         |        | 1         | 開啟            |

|         |        | PT36IE:   | PT36 外部中斷致能控制 |

| Bit[22] | PT36IE | 0         | 關閉            |

|         |        | 1         | 開啟            |

|         |        | PT35IE:   | PT35 外部中斷致能控制 |

| Bit[21] | PT35IE | 0         | 關閉            |

|         |        | 1         | 開啟            |

|         |        | PT34IE:   | PT34 外部中斷致能控制 |

| Bit[20] | PT34IE | 0         | 關閉            |

|         |        | 1         | 開啟            |

|         |        | PT33IE:   | PT33 外部中斷致能控制 |

| Bit[19] | PT33IE | 0         | 關閉            |

|         |        | 1         | 開啟            |

|         |        | PT32IE:   | PT32 外部中斷致能控制 |

| Bit[18] | PT32IE | 0         | 關閉            |

|         |        | 1         | 開啟            |

|         |        | PT31IE:   | PT31 外部中斷致能控制 |

| Bit[17] | PT31IE | 0         | 關閉            |

|         |        | 1         | 開啟            |

|         |        | PT30IE:   | PT30 外部中斷致能控制 |

| Bit[16] | PT30IE | 0         | 關閉            |

|         |        | 1         | 開啟            |

UG-HY16F3981-V07\_TC

|           |        |                      | ) 中斷請求      |  |

|-----------|--------|----------------------|-------------|--|

| Bit[15:8] | PT3 IR | 0                    | 正常          |  |

|           |        | 1                    | 中斷          |  |

|           |        | PT37IF : F           | PT37 外部中斷旗標 |  |

| Bit[07]   | PT37IF | 0                    | 正常          |  |

|           |        | 1                    | PT37 外部發生中斷 |  |

|           | PT36IF | PT36IF : F           | PT36 外部中斷旗標 |  |

| Bit[06]   |        | 0                    | 正常          |  |

|           |        | 1                    | PT36 外部發生中斷 |  |

|           |        | PT35IF : PT35 外部中斷旗標 |             |  |

| Bit[05]   | PT35IF | 0                    | 正常          |  |

|           |        | 1                    | PT35 外部發生中斷 |  |

| 位元      | 名稱     | 描述         |             |  |  |  |

|---------|--------|------------|-------------|--|--|--|

|         |        | PT34IF : F | PT34 外部中斷旗標 |  |  |  |

| Bit[04] | PT34IF | 0          | 正常          |  |  |  |

|         |        | 1          | PT34 外部發生中斷 |  |  |  |

|         |        | PT33IF : F | PT33 外部中斷旗標 |  |  |  |

| Bit[03] | PT33IF | 0          | 正常          |  |  |  |

|         |        | 1          | PT33 外部發生中斷 |  |  |  |

|         |        | PT32IF : F | PT32 外部中斷旗標 |  |  |  |

| Bit[02] | PT32IF | 0          | 正常          |  |  |  |

|         |        | 1          | PT32 外部發生中斷 |  |  |  |

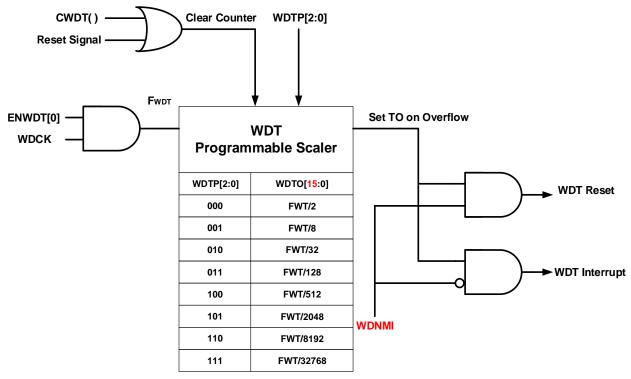

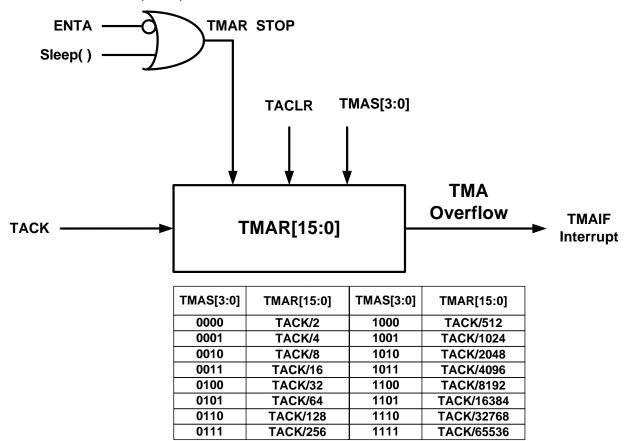

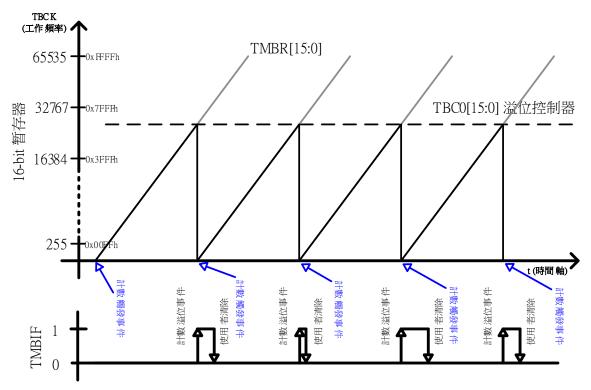

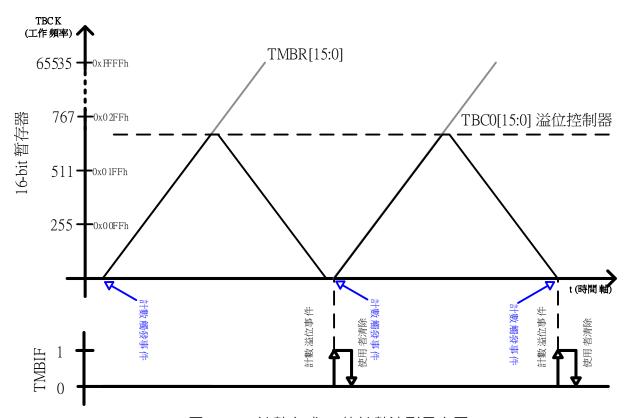

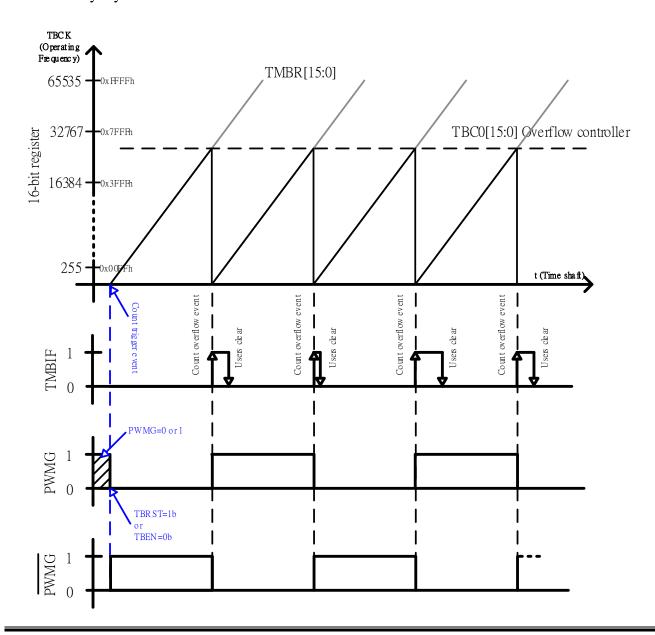

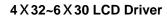

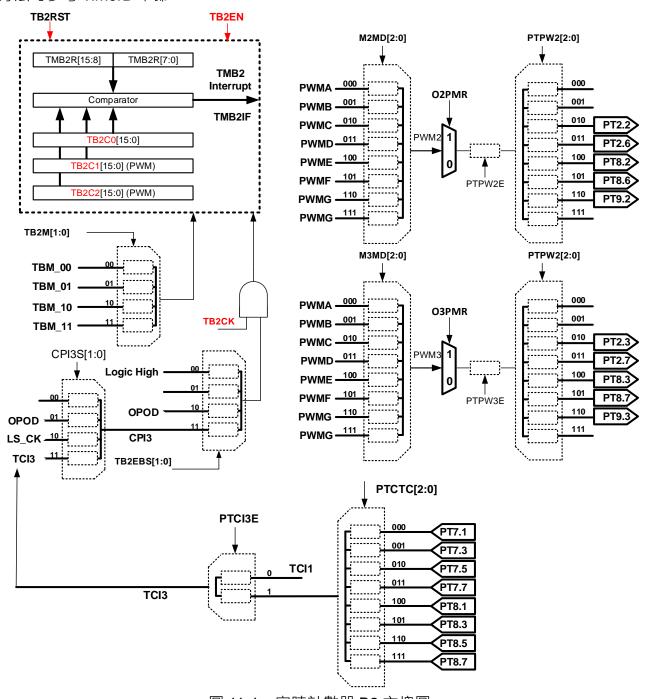

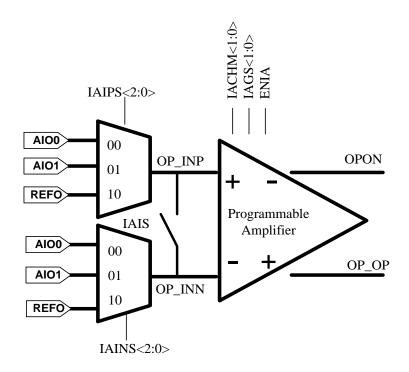

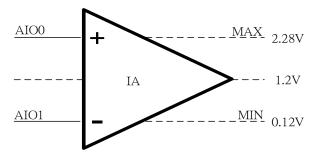

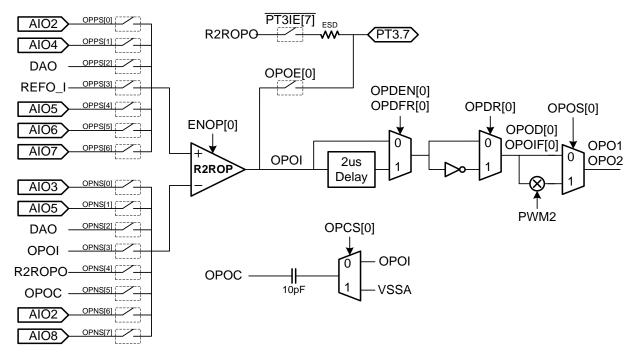

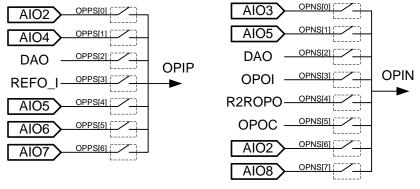

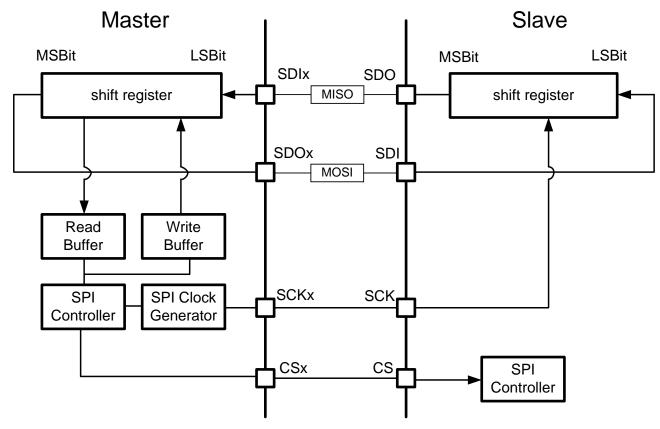

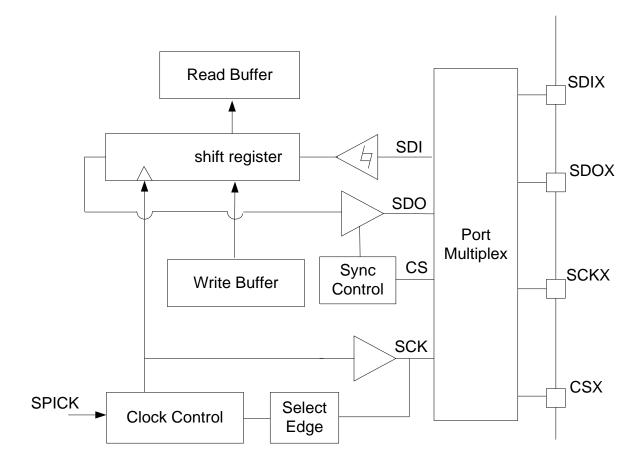

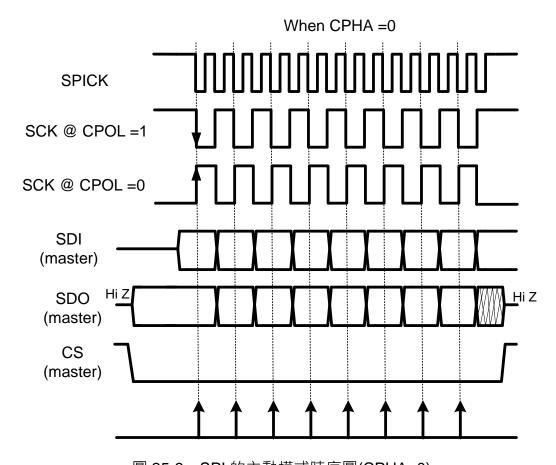

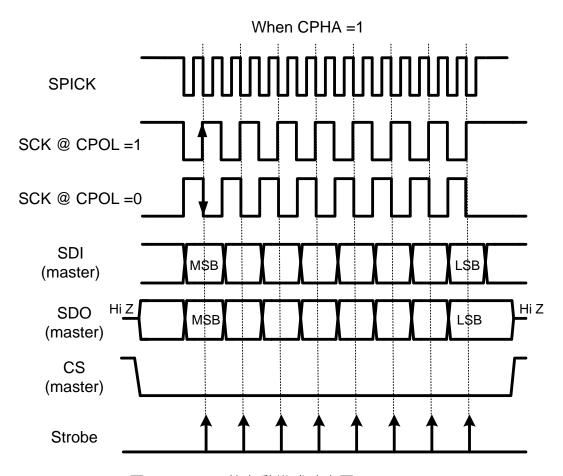

|         |        | PT31IF : F | PT31 外部中斷旗標 |  |  |  |